DAC col TDA1541A per CD723 (o altri CD Philips)

-

andypairo

- sostenitore

- Messaggi: 689

- Iscritto il: 03 nov 2005, 23:17

- Località: Italy

Anche se lo paghi il giusto 8$ e mezzo non sono pochini per un opamp (seppur eccezionale).

Pensando di adoperarlo per tutte le alimentazioni necessarie al progetto credo aumenterebbe troppo il costo, per cui mi limiterei appunto all'alimentazione del clock o, se vogliamo esagerare, alle alimentazioni del DAC (ma ho dei dubbi)

Ciao

Andrea

Pensando di adoperarlo per tutte le alimentazioni necessarie al progetto credo aumenterebbe troppo il costo, per cui mi limiterei appunto all'alimentazione del clock o, se vogliamo esagerare, alle alimentazioni del DAC (ma ho dei dubbi)

Ciao

Andrea

-

andypairo

- sostenitore

- Messaggi: 689

- Iscritto il: 03 nov 2005, 23:17

- Località: Italy

Ho aggiornato lo schema (in allegato come PDF) usando il flea per l'alimentazione del clock e rimanendo con i TL431 per il resto.

Rimane una problematica per i caps di bypass del TDA1541A: io propenderei per un valore più alto dei 100nF classici, magari un 220nF.

Il problema è che i 100nF si trovano anche in case 1210 mentre i 220n solo in case 1812 e superiori. Tradotto in soldoni con i 1210 si riesce a metterli tutti dallo stesso lato del PCB mentre i 1812 sono troppo larghi per la spaziatura tra i pin e andrebbero montati alternati uno lato saldature e uno lato componenti.

In alternativa si possono usare due 100nF 1210 in piggyback e riservare un po' di spazio in più per il pin del MSB.

Marco visto che i PCB sono "roba tua" dammi il tuo parere che poi ti mando i file eagle per lo sbroglio.

Ciao

Andrea

Allegato: DEM_Reclock.pdf ( 108055bytes )

Allegato: DEM_Reclock.pdf ( 108055bytes )

Edit: spulciando su digikey ho visto che si trovano caps fino a 1uF in case 1210 ma sono di tipo "stacked" e non PPS: secondo voi sono peggiori o sono un'alternativa adatta?

Rimane una problematica per i caps di bypass del TDA1541A: io propenderei per un valore più alto dei 100nF classici, magari un 220nF.

Il problema è che i 100nF si trovano anche in case 1210 mentre i 220n solo in case 1812 e superiori. Tradotto in soldoni con i 1210 si riesce a metterli tutti dallo stesso lato del PCB mentre i 1812 sono troppo larghi per la spaziatura tra i pin e andrebbero montati alternati uno lato saldature e uno lato componenti.

In alternativa si possono usare due 100nF 1210 in piggyback e riservare un po' di spazio in più per il pin del MSB.

Marco visto che i PCB sono "roba tua" dammi il tuo parere che poi ti mando i file eagle per lo sbroglio.

Ciao

Andrea

Edit: spulciando su digikey ho visto che si trovano caps fino a 1uF in case 1210 ma sono di tipo "stacked" e non PPS: secondo voi sono peggiori o sono un'alternativa adatta?

-

andypairo

- sostenitore

- Messaggi: 689

- Iscritto il: 03 nov 2005, 23:17

- Località: Italy

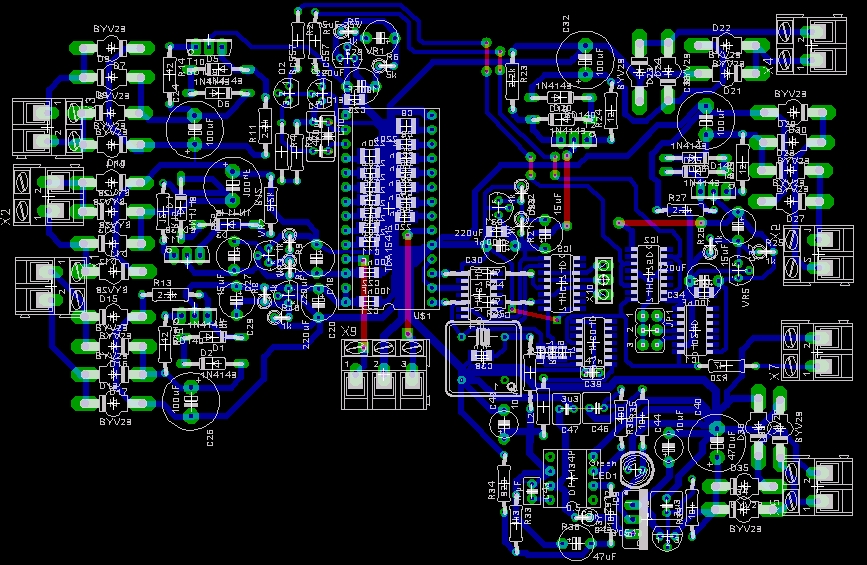

Approfittando di qualche trasferta (e relative serate in albergo...) ho portato avanti lo sbroglio della PCB.

Ho cercato di rimanere sul monofaccia (con qualche ponticello) per riservare il "top" layer al ground plane.

Accetto commenti e consigli, visto che non ho molta esperienza a riguardo. Lo schema è nel post precedente.

Ciao

Andrea

Ho cercato di rimanere sul monofaccia (con qualche ponticello) per riservare il "top" layer al ground plane.

Accetto commenti e consigli, visto che non ho molta esperienza a riguardo. Lo schema è nel post precedente.

Ciao

Andrea

-

andypairo

- sostenitore

- Messaggi: 689

- Iscritto il: 03 nov 2005, 23:17

- Località: Italy

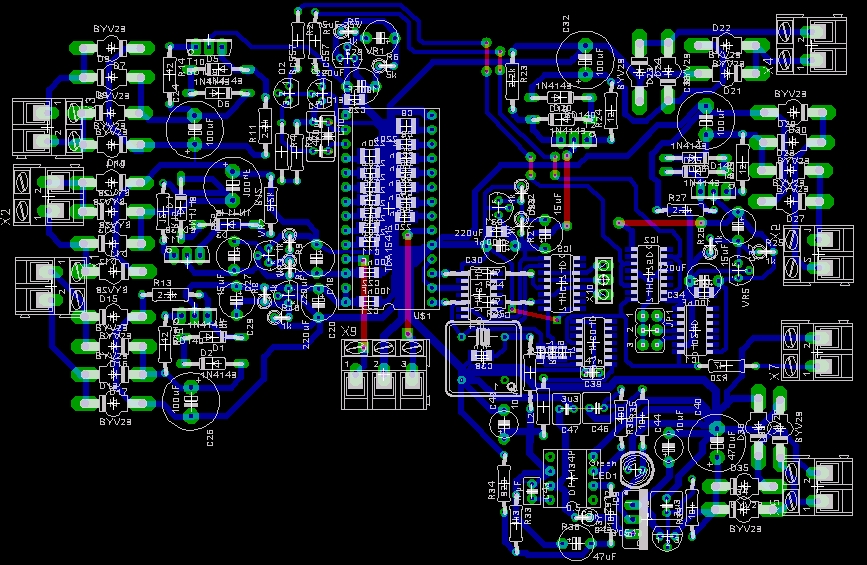

Ho rivisto sostanzialmente lo sbroglio, cercando di mettere le connessioni di alimentazione tutte da un lato.

Non mi sembra malaccio ma sicuramente è migliorabile.

Ora, visto che il progetto è partito come collaborazione su pungolo di Marco ma che finora, a parte i contributi visibili nel thread ho portato avanti tutto io, vorrei capire se ha senso sviluppare ulteriormente il progetto in solitaria

Avrei bisogno di aiuto per l'affinamento dello sbroglio e la produzione della PCB prototipo. Io mi farei carico dei componenti e dei test.

Una volta testato il tutto con risultati soddisfacenti possiamo vedere di fare delle PCB "definitive".

Qualcuno si offre di darmi una mano?

Ciao

Andrea

Non mi sembra malaccio ma sicuramente è migliorabile.

Ora, visto che il progetto è partito come collaborazione su pungolo di Marco ma che finora, a parte i contributi visibili nel thread ho portato avanti tutto io, vorrei capire se ha senso sviluppare ulteriormente il progetto in solitaria

Avrei bisogno di aiuto per l'affinamento dello sbroglio e la produzione della PCB prototipo. Io mi farei carico dei componenti e dei test.

Una volta testato il tutto con risultati soddisfacenti possiamo vedere di fare delle PCB "definitive".

Qualcuno si offre di darmi una mano?

Ciao

Andrea

-

titano

- sostenitore

- Messaggi: 1069

- Iscritto il: 07 ott 2005, 22:35

- Località: Italy

[quote

Ora, visto che il progetto è partito come collaborazione su pungolo di Marco ma che finora, a parte i contributi visibili nel thread ho portato avanti tutto io, vorrei capire se ha senso sviluppare ulteriormente il progetto in solitaria

Avrei bisogno di aiuto per l'affinamento dello sbroglio e la produzione della PCB prototipo. Io mi farei carico dei componenti e dei test.

[/quote]

Se hai notato il numero di post a mio nome e la produttività dimostrata negli ultimi sei mesi credo non sia difficoltoso comprendere che non si è trattato di "razziasmo", semplicemente non ho avuto modi di ritagliarmi alcuno spazio per dedicarmi al diy, in generale.

Spero di avere più tempo a giugno, ma dicevo la stessa cosa di marzo...aprile...maggio...

Per la produzione della pcb prototipo ci penso io, non dovrebbero essereci particolari problemi.

Se ho capito bene il circuito è "a posto" e resta da sistemare la pcb, giusto? Una cosa che ti domandai già tempo fa, senza per altro avere risposta, è se hai considerato le dimensioni del telaio e il posizionamento dei collegamenti che dovrai fare, oltre a distribuire i componenti al fine di semplificare lo sbroglio...

Vista la completa revisione immagino che la domanda non fosse caduta nel vuoto.

Marco

Ora, visto che il progetto è partito come collaborazione su pungolo di Marco ma che finora, a parte i contributi visibili nel thread ho portato avanti tutto io, vorrei capire se ha senso sviluppare ulteriormente il progetto in solitaria

Avrei bisogno di aiuto per l'affinamento dello sbroglio e la produzione della PCB prototipo. Io mi farei carico dei componenti e dei test.

[/quote]

Se hai notato il numero di post a mio nome e la produttività dimostrata negli ultimi sei mesi credo non sia difficoltoso comprendere che non si è trattato di "razziasmo", semplicemente non ho avuto modi di ritagliarmi alcuno spazio per dedicarmi al diy, in generale.

Spero di avere più tempo a giugno, ma dicevo la stessa cosa di marzo...aprile...maggio...

Per la produzione della pcb prototipo ci penso io, non dovrebbero essereci particolari problemi.

Se ho capito bene il circuito è "a posto" e resta da sistemare la pcb, giusto? Una cosa che ti domandai già tempo fa, senza per altro avere risposta, è se hai considerato le dimensioni del telaio e il posizionamento dei collegamenti che dovrai fare, oltre a distribuire i componenti al fine di semplificare lo sbroglio...

Vista la completa revisione immagino che la domanda non fosse caduta nel vuoto.

Guarda, senza promettere nulla spero di riuscire ad essere più attivo tra un paio di settimane...Qualcuno si offre di darmi una mano?

Marco

Marco

-

andypairo

- sostenitore

- Messaggi: 689

- Iscritto il: 03 nov 2005, 23:17

- Località: Italy

Ciao, rispondo solo ora perchè nel thread non si vedeva nulla ma nel fare il "reply" ho trovato la tua risposta (che può essere successo?)Se hai notato il numero di post a mio nome e la produttività dimostrata negli ultimi sei mesi credo non sia difficoltoso comprendere che non si è trattato di "razziasmo", semplicemente non ho avuto modi di ritagliarmi alcuno spazio per dedicarmi al diy, in generale.

Spero di avere più tempo a giugno, ma dicevo la stessa cosa di marzo...aprile...maggio...

Per la produzione della pcb prototipo ci penso io, non dovrebbero essereci particolari problemi.

Se ho capito bene il circuito è "a posto" e resta da sistemare la pcb, giusto? Una cosa che ti domandai già tempo fa, senza per altro avere risposta, è se hai considerato le dimensioni del telaio e il posizionamento dei collegamenti che dovrai fare, oltre a distribuire i componenti al fine di semplificare lo sbroglio...

Vista la completa revisione immagino che la domanda non fosse caduta nel vuoto.

Guarda, senza promettere nulla spero di riuscire ad essere più attivo tra un paio di settimane...Qualcuno si offre di darmi una mano?

Marco

Originally posted by titano - 23/05/2007 : 12:01:19

Dunque il circuito è *abbastanza* a posto, nel senso che va provato e potrebbero essere necessari dei cambiamenti, specie per quel che riguarda il DEM reclock. La disposizione ad ora non è particolarmente studiata per il 723, perchè pensavo di fare una PCB "universale" anche per altri CD player e i segnali in comune col 723 sono, a meno di rifare anche le alimentazioni e quindi di eliminare la basetta AF, le 3 linee IIS e il clock al trasporto.

Il primo passo credo sia di verificare che le cose siano a posto dal punto di vista elettrico, per poi passare a studiare l'integrabilità nel player (che comunque ha molto spazio)

Marco, non era un attacco nei tuoi confronti quanto piuttosto un piccolo "sfogo" e un tentativo di trovare altri che potessero aiutare la causa

Ti mando a breve i file eagle.

Ciao

Andrea

-

STEBIL

- new member

- Messaggi: 2

- Iscritto il: 16 dic 2006, 17:20

- Località: Italy

Buongiorno a tutti , questo è il mio primo messaggio in questo forum , un saluto in particolare ad Andrea , che mi ha suggerito questo sito e spedito i chip

Da vari anni sto anche su www.diyaudio.com come stefanobilliani .

Dunque son spinto a postare su questo topic a causa di questo piccolo lettore CD723 che uso ormai da tempo.

Ma le considerazioni delle quali mi accingo a scrivere arrivano dall'ascolto del Marantz CD67 mk2SE in particolare . A parte il fatto che considero il CD723 molto piu silenzioso del CD67 - e già questo mi fa automaticamente virare sul

723 , trovo dall'altro lato della vicenda che il Marantz lascia intravedere una maggior fluidità nel timing con vari effeti benefici , che se non fosse per il rumore potrebbero venir felicemente a galla .

Quindi dopo essermi posto alcune domande ho dato un'occhiata a come sono "motorizzati" ripsettivamente lo Saa7378 ( cd 723 ) e Saa7372 ( cd67 ). Entrambi i decoder hanno una cosa in comune: se l'input è un clock a 8.4672Mhz hanno bisogno di un PLL interno che moltiplica la frequenza . Con lo stesso valore di registro ( registro B ) l'input puo essere sia 8.4672Mhz che 33.8688Mz . Usando 8.4672 Mhz va attivato il PLL interno tramite SELPLL posto al valore " 1" .

Per usare anche la frequenza 16.9344 Mhz si rende necessario modificare il registro " B" che come sappiamo non è una cosa cosi immediata .

Bene , detto questo .. il CD67 lavora a 16.9344 con il PLL interno disattivato , ma il bello è che possiamo disattivare sto PLL anche nel CD723 - senza modificare il registro - solo settando SELPLL a "O" e utilizzando un Xo a 33.8688 Mhz . Se qualcuno facesse delle misure di jitter sui segnali del 723 son convinto che risulterebbero piu decenti nella soluzione senza PLL . Analogamente cosi com'è il 723 produce un suono un po "stressato " attribuibile a valori di jitter non ottimali... ed il CD67 "suona " meglio pur in quell'ambiente cosi rumoroso ...beh alcuni produttori discografici riportano spesso di come possa suonare bene un sistema con clock NON PLL !

Ho già ordinato da Tentlabs un Xo per lo scopo , il resto ve lo saprò raccontare dopo i test

Ultima cosa , a differenza di altri player il 723 a me sembra piu felice con segnali I2S e Xo attorno ai 1.4- 1.7 volt DC , cio per dire che il Tent Xo preferisco alimentarlo a3.3 volt in questa applicazione - stile DVD player

Stessa cosa per i circuiti di reclock .

Ok grazie per l'ascolto e a presto

Stefano

Da vari anni sto anche su www.diyaudio.com come stefanobilliani .

Dunque son spinto a postare su questo topic a causa di questo piccolo lettore CD723 che uso ormai da tempo.

Ma le considerazioni delle quali mi accingo a scrivere arrivano dall'ascolto del Marantz CD67 mk2SE in particolare . A parte il fatto che considero il CD723 molto piu silenzioso del CD67 - e già questo mi fa automaticamente virare sul

723 , trovo dall'altro lato della vicenda che il Marantz lascia intravedere una maggior fluidità nel timing con vari effeti benefici , che se non fosse per il rumore potrebbero venir felicemente a galla .

Quindi dopo essermi posto alcune domande ho dato un'occhiata a come sono "motorizzati" ripsettivamente lo Saa7378 ( cd 723 ) e Saa7372 ( cd67 ). Entrambi i decoder hanno una cosa in comune: se l'input è un clock a 8.4672Mhz hanno bisogno di un PLL interno che moltiplica la frequenza . Con lo stesso valore di registro ( registro B ) l'input puo essere sia 8.4672Mhz che 33.8688Mz . Usando 8.4672 Mhz va attivato il PLL interno tramite SELPLL posto al valore " 1" .

Per usare anche la frequenza 16.9344 Mhz si rende necessario modificare il registro " B" che come sappiamo non è una cosa cosi immediata .

Bene , detto questo .. il CD67 lavora a 16.9344 con il PLL interno disattivato , ma il bello è che possiamo disattivare sto PLL anche nel CD723 - senza modificare il registro - solo settando SELPLL a "O" e utilizzando un Xo a 33.8688 Mhz . Se qualcuno facesse delle misure di jitter sui segnali del 723 son convinto che risulterebbero piu decenti nella soluzione senza PLL . Analogamente cosi com'è il 723 produce un suono un po "stressato " attribuibile a valori di jitter non ottimali... ed il CD67 "suona " meglio pur in quell'ambiente cosi rumoroso ...beh alcuni produttori discografici riportano spesso di come possa suonare bene un sistema con clock NON PLL !

Ho già ordinato da Tentlabs un Xo per lo scopo , il resto ve lo saprò raccontare dopo i test

Ultima cosa , a differenza di altri player il 723 a me sembra piu felice con segnali I2S e Xo attorno ai 1.4- 1.7 volt DC , cio per dire che il Tent Xo preferisco alimentarlo a3.3 volt in questa applicazione - stile DVD player

Stessa cosa per i circuiti di reclock .

Ok grazie per l'ascolto e a presto

Stefano

-

STEBIL

- new member

- Messaggi: 2

- Iscritto il: 16 dic 2006, 17:20

- Località: Italy

Ecco mi rendo ora conto rileggendo il thread che l'argomento è stato già sfiorato da Andrea proprio agli inizi .-il filtro digitale usa un PLL per ricavare una frequenza multipla di 8.4 Mhz per lavorare ed esiste la possibilità di usare un clock a 33.2 MHz disattivando il PLL interno. Sicuramente senza reclock ci sarebbe un vantaggio ma visto che riclocchiamo i dati non credo si abbiano grossi vantaggi

Ciao

Andrea

Originariamente inviato da andypairo - 27/10/2006 : 21:35:12

Beh dopo ripetuti ascolti , credo che la mia personale scelta andrebbe ( e poi verificherò "sul campo " ) sulla situazione NO PLL , a dipendere da reclock oppure no . Anche perchè in tutta meditazione , non credo che il problema di questo PLL si rifletta direttamente tanto sulla qualità del BCK ( il quale è facilmente sostituibile dividendo o ricloccando ) ma tanto sul comportamento generico all'interno del chip decorder stesso , Data slicer . E poi uscite a 11 mhz per controlli esterni . Bisognerebbe andare a fondo all'interno dell'architettura del chip per spiegare bene. In ogni modo in modalità 4*Fs il formato funziona anche col BCK direttamente dall'XO , non v'è dubbio , e se attaccare il BCK direttamente all'XO da un senso di "sicurezza " non mi sembra risolvere alcuni problemi insiti di questo lettore Come dire che c'è effettivamente qualcosa d'altro che stressa .

Vi terrò informati del risultato .

Cha chao .

Stefano

-

andypairo

- sostenitore

- Messaggi: 689

- Iscritto il: 03 nov 2005, 23:17

- Località: Italy

Innanzitutto benvenuto Stefano,

sono contento che sei approdato al nostro forum.

Ne approfitto per chiederti di spiegare in un post come hai modificato le alimentazioni del CD723, in modi che sia di riferimento per chi intendesse modificarlo.

Ho ancora la mail che mi hai mandato a novembre ma mancano dei dettagli e poi credo sia più giusto che sia tu a parlare del tuo lavoro

Ciao

Andrea

sono contento che sei approdato al nostro forum.

Ne approfitto per chiederti di spiegare in un post come hai modificato le alimentazioni del CD723, in modi che sia di riferimento per chi intendesse modificarlo.

Ho ancora la mail che mi hai mandato a novembre ma mancano dei dettagli e poi credo sia più giusto che sia tu a parlare del tuo lavoro

Ciao

Andrea

-

andypairo

- sostenitore

- Messaggi: 689

- Iscritto il: 03 nov 2005, 23:17

- Località: Italy

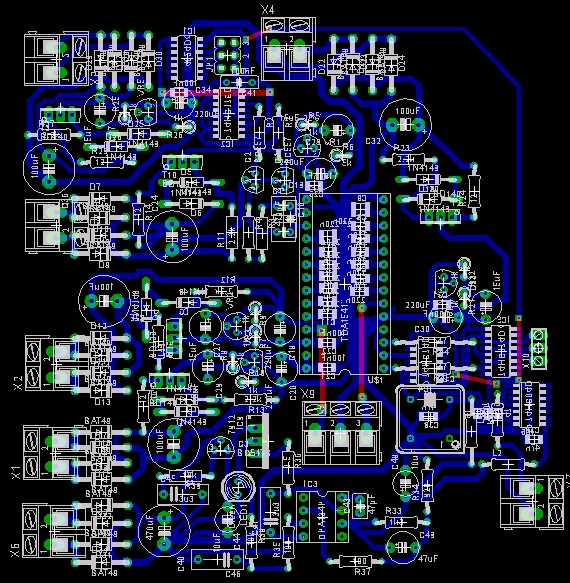

Ecco la terza versione beta della PCB (tutto va ancora provato).

Ciao

Andrea

Attachment: SchemiPcbv3.zip ( 50057bytes )

Attachment: SchemiPcbv3.zip ( 50057bytes )

Ciao

Andrea

-

titano

- sostenitore

- Messaggi: 1069

- Iscritto il: 07 ott 2005, 22:35

- Località: Italy

C'è qualche pista interrotta e qualche appendice in eccesso. Puoi ricontrollare un attimo? Nascondi il layout componenti, dovresti notarle più facilmenteA questo punto direi di sì ; )

Poi, una volta verificato il tutto possiamo pensare ad ulteriori modifiche.

Ciao

Andrea

Originally posted by andypairo - 19/06/2007 : 19:56:04

Marco

Marco

-

andypairo

- sostenitore

- Messaggi: 689

- Iscritto il: 03 nov 2005, 23:17

- Località: Italy

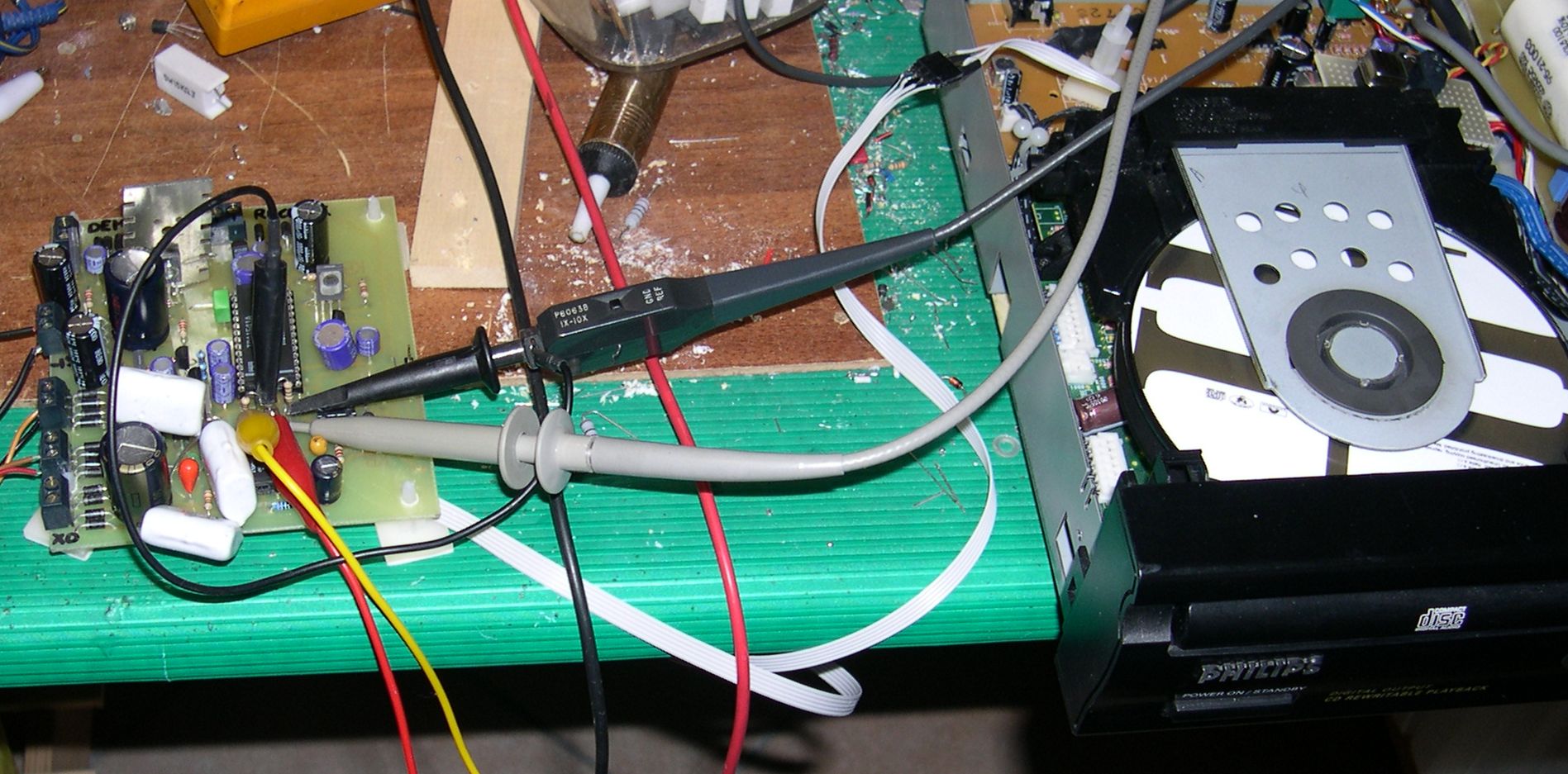

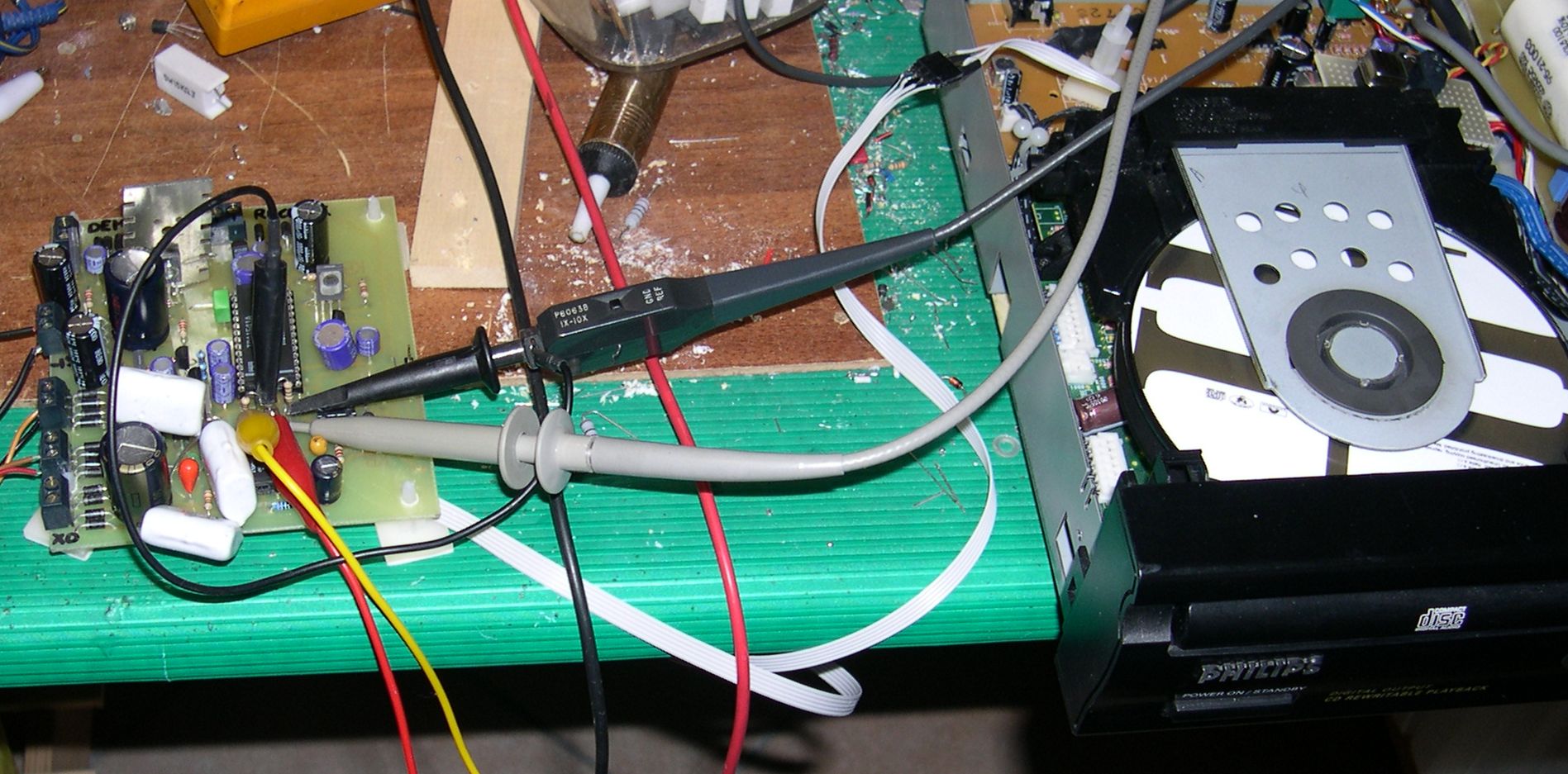

Dopo una lunga attesa siamo giunti ai primi test.

Fase 1: TDA nudo e crudo, pilotato dal CD723 hackerato.

Il formato è IIS ma la lunghezza dei frame 48Fs invece dei consueti 64.

Dopo un empasse iniziale.. funziona. Stadio I/V: R da 15 Ohm, poi diretto sul my_ref (ovviamente solo per prova).

Prime pics:

Fase 1: TDA nudo e crudo, pilotato dal CD723 hackerato.

Il formato è IIS ma la lunghezza dei frame 48Fs invece dei consueti 64.

Dopo un empasse iniziale.. funziona. Stadio I/V: R da 15 Ohm, poi diretto sul my_ref (ovviamente solo per prova).

Prime pics:

-

andypairo

- sostenitore

- Messaggi: 689

- Iscritto il: 03 nov 2005, 23:17

- Località: Italy

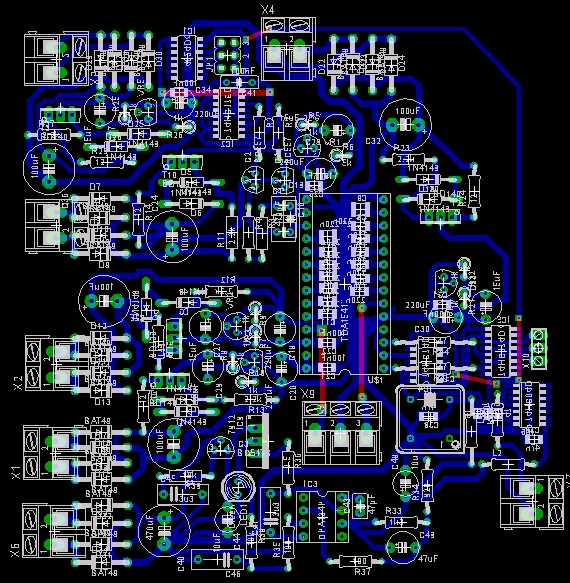

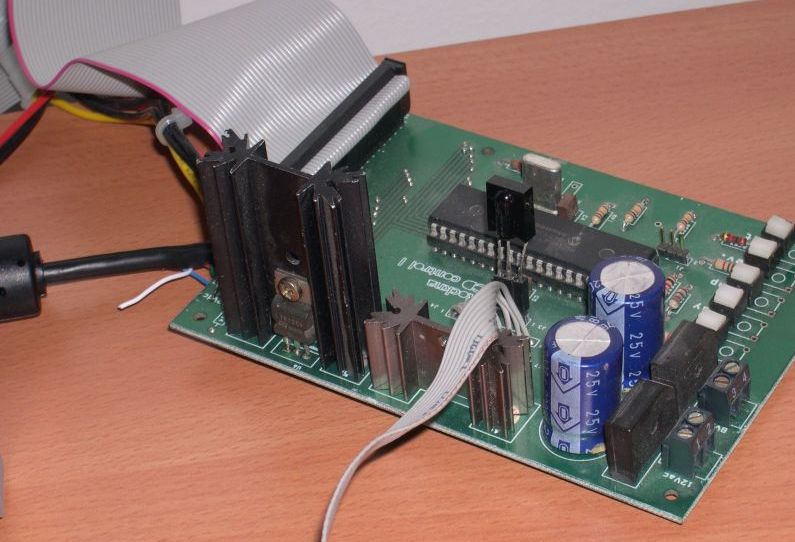

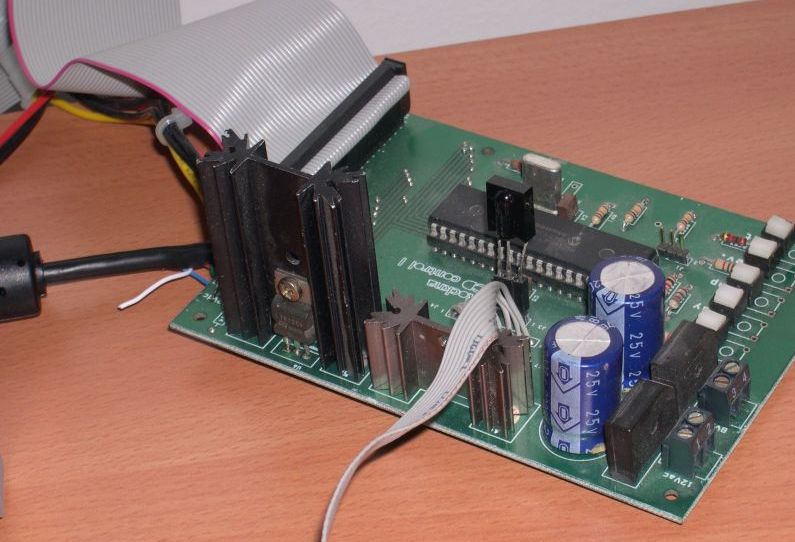

Foto della PCB: notare i caps SMD per il decoupling del DEM. Per errore ho ricevuto dei 1210 al posto dei 1206 previsti e ho dovuto montarli sul fianco

Prossimo step: inserire il FLEA e il Tent XO.

Non prevedo problemi perchè adesso il CD usa già un XO, si tratta solo di collegarlo a quello sulla PCB.

A riguardo... ho preso una sòla.. comprati degli AD797 a otimo prezzo, arrivano e sono marchiati in maniera insolita... quando li provo non va nulla

Per ora uso un OPA627. PS se qualcuno ha dei Wima MKS2 da 3,3uF 50V o 63V o altre marche ma a passo max 7.5mm me ne servirebbero alcuni pezzi...

Ciao

Andrea

Prossimo step: inserire il FLEA e il Tent XO.

Non prevedo problemi perchè adesso il CD usa già un XO, si tratta solo di collegarlo a quello sulla PCB.

A riguardo... ho preso una sòla.. comprati degli AD797 a otimo prezzo, arrivano e sono marchiati in maniera insolita... quando li provo non va nulla

Per ora uso un OPA627. PS se qualcuno ha dei Wima MKS2 da 3,3uF 50V o 63V o altre marche ma a passo max 7.5mm me ne servirebbero alcuni pezzi...

Ciao

Andrea

-

andypairo

- sostenitore

- Messaggi: 689

- Iscritto il: 03 nov 2005, 23:17

- Località: Italy

Fase 2: inserito il tent XO e il Flea

Primo errore: devo aver involontariamente specchiato il pinout del Tent XO, per cui mi tocca montarlo dal lato saldature.

Per fortuna lavora ancora

Il player funziona ancora, per cui passo a inserire il reclock.

Secondo errore: ho dimenticato aperti i pin di clear dei flip flop, che vanno portati a +5.

Rimediato a questo errore il reclock va bene a 1xFs e 2xFs.

a 4xFs il BCK (che è alla stessa frequenza del clock) non viene ricloccato correttamente. Forse è legato al collegamento lungo e poco adatto (flat cable di circa 50cm, la forma d'onda è alquanto distorta). Verificherò.

Ciao

Andrea

Primo errore: devo aver involontariamente specchiato il pinout del Tent XO, per cui mi tocca montarlo dal lato saldature.

Per fortuna lavora ancora

Il player funziona ancora, per cui passo a inserire il reclock.

Secondo errore: ho dimenticato aperti i pin di clear dei flip flop, che vanno portati a +5.

Rimediato a questo errore il reclock va bene a 1xFs e 2xFs.

a 4xFs il BCK (che è alla stessa frequenza del clock) non viene ricloccato correttamente. Forse è legato al collegamento lungo e poco adatto (flat cable di circa 50cm, la forma d'onda è alquanto distorta). Verificherò.

Ciao

Andrea

-

andypairo

- sostenitore

- Messaggi: 689

- Iscritto il: 03 nov 2005, 23:17

- Località: Italy

Ciao,

ho verificato col progettista della sezione di reclock e in effetti non è possibile riicloccare un segnale da 8.x Mhz con un clock della stessa frequenza. Esiste la possibilità di adoperare direttamente il clock come BCK (previa modifica dello stampato e inserzione di un jumper per la selezione) ma per il momento mi accontento di 1xFs e 2xFs.

Per ultimo ho inserito il DEM reclock, non prima di aver corretto un errore sullo stampato e dopo alcuni tentativi (un elettrolitico inserito al contrario

e dopo alcuni tentativi (un elettrolitico inserito al contrario  , meno male che stavo usando l'alimentatore da banco e mi sono accorto subito) il tutto sembra funzionare correttamente. La frequenza del DEM reclock è l'unica possibile con il clock di partenza nel range attorno ai 200kHz (264kHz), pari a 6xFs.

, meno male che stavo usando l'alimentatore da banco e mi sono accorto subito) il tutto sembra funzionare correttamente. La frequenza del DEM reclock è l'unica possibile con il clock di partenza nel range attorno ai 200kHz (264kHz), pari a 6xFs.

Con un player che usi un data frame di 64xFs (IIS "standard") si potrebbe scegliere tra 4 e 8xFs.

L'esperimento alla fine sembra riuscito.

Ora devo mettere insieme un I/V come si deve e verificare alcune cosucce.

Per gli esperti di misure con l'oscillo (ho a disposizione un TEK 2246 100 Mhz - 4 canali e 2 sonde Tektronix 1:10 di cui una switchabile 1:1) che accortezze devo adoperare per ottenere delle misure attendibili sulla pulizia delle alimentazioni, sui ringing, ecc?

Lo chiedo perchè adesso se inverto le sonde (di cui una sola ha la massa collegata) il medesimo segnale viene visto in maniera piuttosto differente per quanto riguarda il rumore/oscillazione sovrapposti.

Conviene forse fare un collegamento unico alla boccola di terra ?

Ciao

Andrea

ho verificato col progettista della sezione di reclock e in effetti non è possibile riicloccare un segnale da 8.x Mhz con un clock della stessa frequenza. Esiste la possibilità di adoperare direttamente il clock come BCK (previa modifica dello stampato e inserzione di un jumper per la selezione) ma per il momento mi accontento di 1xFs e 2xFs.

Per ultimo ho inserito il DEM reclock, non prima di aver corretto un errore sullo stampato

Con un player che usi un data frame di 64xFs (IIS "standard") si potrebbe scegliere tra 4 e 8xFs.

L'esperimento alla fine sembra riuscito.

Ora devo mettere insieme un I/V come si deve e verificare alcune cosucce.

Per gli esperti di misure con l'oscillo (ho a disposizione un TEK 2246 100 Mhz - 4 canali e 2 sonde Tektronix 1:10 di cui una switchabile 1:1) che accortezze devo adoperare per ottenere delle misure attendibili sulla pulizia delle alimentazioni, sui ringing, ecc?

Lo chiedo perchè adesso se inverto le sonde (di cui una sola ha la massa collegata) il medesimo segnale viene visto in maniera piuttosto differente per quanto riguarda il rumore/oscillazione sovrapposti.

Conviene forse fare un collegamento unico alla boccola di terra ?

Ciao

Andrea

-

campedel

- starting member

- Messaggi: 209

- Iscritto il: 07 feb 2006, 16:25

- Località: Italy - Bologna

- Been thanked: 1 time

- Contatta:

Se sei interessato a misurare il rumore a frequenza elevata, usa una sonda alla volta, con la massa collegata il più vicino possibile al puntale della sonda (ad es. ai capi di un condensatore). Può essere utile attorcigliare il filo con il coccodrillo di massa attorno al puntale della sonda, ed eventualmente avvolgere il cavo della sonda attorno ad un nucleo di ferrite (quelli composti da due seminuclei tipo RM o ETD sono particolarmente comodi).Per gli esperti di misure con l'oscillo (ho a disposizione un TEK 2246 100 Mhz - 4 canali e 2 sonde Tektronix 1:10 di cui una switchabile 1:1) che accortezze devo adoperare per ottenere delle misure attendibili sulla pulizia delle alimentazioni, sui ringing, ecc?

Lo chiedo perchè adesso se inverto le sonde (di cui una sola ha la massa collegata) il medesimo segnale viene visto in maniera piuttosto differente per quanto riguarda il rumore/oscillazione sovrapposti.

Conviene forse fare un collegamento unico alla boccola di terra ?

Originally posted by andypairo - 13/10/2007 : 15:39:32

Ciao

Francesco

Ciao

Francesco

==================================

When people believe in boundaries, they become part of them

Francesco

==================================

When people believe in boundaries, they become part of them

-

andypairo

- sostenitore

- Messaggi: 689

- Iscritto il: 03 nov 2005, 23:17

- Località: Italy

Ciao,

ho dato un'occhiata alle alimentazioni e sono rimasto un po' interdetto: quasi tutti i 5V (a parte il +5 del TDA) presentano un'oscillazione a dente di sega intorno ai 5 kHz e ampiezza 30-40mV pk-pk. Il -15 presenta un'oscillazione più elevata e a frequenza inferiore.

Ricordo che sono regolatori shunt basati su TL431 pilotati da un CCS con singolo BJT (circa 60mA), pin ADJ bypassato verso il catodo del TL431 con OSCON da 22uF e in uscita OSCON da 220uF parallelato da 100nF SMD ceramico.

Ho provato a inserire una R tra il CCS e lo shunt senza risultati.

Parallelare caps di piccolo valore non serve, come nemmeno togliere il C di bypass di Vref.

Sostituendo il 220uF OSCON con un 100uF Panasonic FC non ho più oscillazione ma vedo chiaramente gli spike delle commutazioni degli IC (invisibili prima) con un ordine di grandezza di 20-30mV.

Domanda: guardando sul datasheet del TL431 http://focus.ti.com/lit/ds/symlink/tl431.pdf

a pagina 24 abbiamo il grafico di stabilità. Con 220uF dovrei essere più che a posto (col bypass su Vref in AC dobbiamo usare la curva A)... allora come mai mi fa questo scherzo?

Ciao

Andrea

ho dato un'occhiata alle alimentazioni e sono rimasto un po' interdetto: quasi tutti i 5V (a parte il +5 del TDA) presentano un'oscillazione a dente di sega intorno ai 5 kHz e ampiezza 30-40mV pk-pk. Il -15 presenta un'oscillazione più elevata e a frequenza inferiore.

Ricordo che sono regolatori shunt basati su TL431 pilotati da un CCS con singolo BJT (circa 60mA), pin ADJ bypassato verso il catodo del TL431 con OSCON da 22uF e in uscita OSCON da 220uF parallelato da 100nF SMD ceramico.

Ho provato a inserire una R tra il CCS e lo shunt senza risultati.

Parallelare caps di piccolo valore non serve, come nemmeno togliere il C di bypass di Vref.

Sostituendo il 220uF OSCON con un 100uF Panasonic FC non ho più oscillazione ma vedo chiaramente gli spike delle commutazioni degli IC (invisibili prima) con un ordine di grandezza di 20-30mV.

Domanda: guardando sul datasheet del TL431 http://focus.ti.com/lit/ds/symlink/tl431.pdf

a pagina 24 abbiamo il grafico di stabilità. Con 220uF dovrei essere più che a posto (col bypass su Vref in AC dobbiamo usare la curva A)... allora come mai mi fa questo scherzo?

Ciao

Andrea

-

- Argomenti simili

- Risposte

- Visite

- Ultimo messaggio