Pagina 1 di 1

Inviato: 24 ott 2006, 03:24

da andypairo

Discutendo con Marco (Titano) di DAC abbiamo deciso di rovinarci con le nostre mani e di studiare una soluzione che permetta di inserire uno dei migliori DAC mai prodotti, il TDA1541A, all'interno di un CD player "budget" (il CD723 appunto, ma il discorso vale per qualsiasi CD player con formato IIS).

L'idea è di eliminare quello che è considerato l'anello debole della riproduzione digitale, cioè l'interfaccia SPDIF, considerata uno dei maggiori "contributori" del famigerato jiitter.

La prima obiezione è che il CD723 non usa il formato dati IIS, ma un autocostruttore francese (Robinet) ha studiato un "hacker", cioè un dispositivo a microcontrollore che riprogramma il filtro digitale SAA7378 (non ricordo ora) in modo da consentire di ottenere, a scelta il formato IIS o EJAI e pure il fattore di sovracampionamento (1,2 o 4).

Un secondo motivo che ha fatto ricadere la scelta sul CD723 (che si trova su ebay a prezzi modici) è che ci sta un sacco di roba, infatti è praticamente vuoto per 2/3 e ciò consente una certa libertà di azione.

Elenco brevemente le idee base (non farina del mio sacco ma un "collage" di quelle che mi sono sembrate le migliori soluzioni:

-Alimentazioni di tipo shunt con LM431 pilotato da CCS, secondari separati per le varie alimentazioni (almeno analogico e digitale)

-Master clock Low Jitter Tent Labs XO con alimentazione dedicata svolgente le seguenti funzioni:

- reclock dei segnali IIS immediatamente prima del DAC

- sincronizzazione della meccanica

-Eventuale rifacimento dell'alimentazione del CD (cambiando il DAC la basetta originale fa solo da alimentatore

-Conversione I/V e stadio di uscita a scelta tra le varie proposte presenti in rete, io ho provato personalmente quelle di T.Loesch con la E88cc e l'OPA660 ma ce ne sono altre, tipo quelle proposte da Pedja o da Lesha

Alcuni link per vedere i progetti da cui ho tratto ispirazione:

http://belinfabien.free.fr/dac/tda1541a/tda1541a.htm - per la parte di rifacimento della schedina di alimentazione

http://peufeu.free.fr/audio/extremist_d ... ent_1.html per l'ottima descrizione e implementazione del reclock

http://benjamin.silvestre.club.fr/cd723 ... ack_e.html

per l'hacker e una possibile variante di clock

Per oggi è tutto, se avete commenti e proposte sono bene accetti.

Ciao

Andrea

Inviato: 24 ott 2006, 04:16

da titano

Per quanto riguarda la scheda originale, nell'ottica della completa sostituzione della sezione di conversione digitale/analogica con relativo stadio d'uscita, non credo sia sbagliato pensare alla soppressione della suddetta scheda al fine di sostituirla con una contenente solo le alimentazioni di servizio, che nella implementazione originale sono a dir poco "leggerine"...

Ci sono un paio di esempi che possono tornare utili:

http://benjamin.silvestre.club.fr/cd723 ... drive.html

http://benjamin.silvestre.club.fr/cd723 ... sch-32.png

e

http://belinfabien.free.fr/cd/cd723/cd723.htm

http://belinfabien.free.fr/cd/cd723/sch ... cement.png

Marco

Inviato: 24 ott 2006, 14:43

da traferro

scusate se approfito dello spazio, ma sul sito tnt-audio non è chiaro come avvolgere il trafo di ingresso spdif, lui parla di spire con filo per trasformer, senza dire sezione del filo ecc. Qualcuno sarebbe cosi gentile da dirmi qualcosa in piu.

Inviato: 24 ott 2006, 16:23

da mrjam

Ciao

La sezione del filo è l'ultima cosa di cui ti devi preoccupare.

Il trasfo spdif è attraversato da un segnale RF - 2.8Mhz - non è un TU!

Ti consiglio di soffermarti sul materiale del nucleo e sulla tecnica di avvolgimento.

Puoi vedere sul sito Audionote i trasfo toroidali che usano sui dac.

Oppure se hai occasione di ordinare da Digi-key: Newava S22083 o S22133 (schermato) ..costano poco!

Ecco un link che ti può dare qualche info

http://www.arrl.org/qex/2005/qx3Trask.pdf

Buon AudioFaidate!

Ciao

Roberto

Inviato: 24 ott 2006, 17:35

da andypairo

Ritornando on-topic mi sembrava mi fosse sfuggito qualcosa: il DEM reclocking (che non è un reclocking vero e proprio ma piuttosto un "clocking" della macchina interna).

Anche questo direi merita cittadinanza.

Ciao

Andrea

Inviato: 24 ott 2006, 18:11

da PPoli

...basta! lasciatemi lavorare!...

A casa ho giusto giusto una di quelle scatoline che si trovano all'ikea e che uso per eviatre che mia moglie archivi "a suo modo" quello che lascio in giro, con dentro due TDA 1541, un CS8412, minuteria elettronica varia, e per finire una bella coppia di 6c45pi da usare come stadio finale.

Che dite? La tiro fuori.

PS il dac che avevo fatto con 4 TDA1543 non mi ha convinto troppo, ma avevo anche usato componenti scadenti.

Inviato: 24 ott 2006, 18:18

da marziom

mi sa che stiamo facendo un casino.....se ho capito bene il 3d parla di un DAC da mettere dentro il CD723 senza usare il ricevitore e quindi il collo di bottiglia del SPDIF.

PPoli invece parla di un dac con ricevitore........

ma allora?!?!?

vabbè tanto io sono interessato and entrami gli aspetti!

(ho un DAC pronto a da finire e ........ una meccanica NEC + TDA1541 da assiemare senza ricevitore)

Inviato: 24 ott 2006, 18:32

da titano

Vediamo dimettere ordine. L'intenzione è quella di sostituire in toto o quasi l'elettronica di un lettore economico come il 723( che si presta molto bene allo scopo, se non altro per la possibilità di hack e per tutto il materiale di supporto on line che facilità non poco il lavoro).

Niente ricevitori. Niente spdif.

l'idea è quella di trovare un accordo sul tipo di soluzioni da utilizzare per le modifiche di alimentazione, dac, reclok/clock...lascinado poi libertà di intervanto nello stadio analogico.

Ancora interessati?

Marco

Inviato: 24 ott 2006, 19:23

da andypairo

In linea teorica sarebbe anche possibile montare l'SPDIF ma si rinuncerebbe alla possibilità di un reclocking sincrono e ai (grossi) vantaggi che esso comporta, per non parlare della "personalizzazione" che non verrebbe sfruttata.

E poi con 30-40€ la si trova facilmente una "cavia" su ebay.de

Quindi se uno vuole usare la "base" per un DAC esterno lo può fare, a patto di fare da sè per la sezione "ricevitore" e di sapere che non sfrutterà appieno le potenzialità dell'oggetto.

ciao

Andrea

Inviato: 24 ott 2006, 19:42

da marziom

vabbè, io vi seguo ma se ci riesco lavorerò sul NEC...

ma è cosi difficile portare fuori del nostro lettore CD il segnale digitale?

marzio

Inviato: 24 ott 2006, 20:17

da andypairo

Come spiegato nel post di introduzione il lavoro si può ben adattare anche ad altri CD player (o anche CD-ROM....), l'importante è che utilizzino il formato dati IIS.

L'unica eccezione è il CD723 (e l'equivalente modello Marantz) che usa nativamente l'EJAI (o formato Sony) ma è hackerabile.

Per sapere che formato dati usa il tuo CDP devi vedere che DAC monta.

Ciao

Andrea

Inviato: 24 ott 2006, 20:55

da marziom

se non erro CXD2559

che da i datashett che ho e dal service manual....equivale ad avere i segnali BCK (bit clock), SI (DATA) e LRCK

va bene?

marzio

Inviato: 24 ott 2006, 21:32

da andypairo

Non è sufficiente, anche l'EJAI usa questi 3 segnali. L'importante è sapere come sono codificati.

Ciao

Andrea

Inviato: 24 ott 2006, 22:56

da marziom

scusa l'ignoranza, ma come faccio a capire il formato dal datashett del DAC?

marzio

Inviato: 25 ott 2006, 03:37

da PPoli

Nel dac che ho con i TDA1543 ho fatto la sezione ricevitore completamente separata, anche il trasformatore, pronta per essere riutilizzata in un altro progetto. Inoltre ho sempre come idea a lunghissimo temine (quasi un sogno) di utilizzare la spendida cdPro che ha già la sua sezione elettronica con uscita analogica (Dac integrato) o in altenativa I2S.

Questo immagino lo conosciate

http://www.daisy-laser.nl/

La sincronizzazone del clock della meccanica l'avevo capito che è quella che vi solletica maggiormente, ma al momento (chissà che non mi contagiate) non mi smuove particolarmente i sensi. In ogni caso il progetto mi interessa.

Inviato: 25 ott 2006, 14:08

da andypairo

marzio: non sono così esperto ma da qualche parte deve essere scritto, magari non in maniera esplicita.

qui

http://www.geocities.com/nonospcm1704/ trovi una descrizione dei due formati

Un oscilloscopio può esserti molto utile se il datasheet non è chiaro.

paolo: visto che hai la CDPRO... la piazzi in uno dei tuoi bellissimi contenitori e ti fai un CD da sballo!

Una nota riguardo al CD723: ieri sera stavo preparando il post in cui descrivevo le scelte da effettuare per la sezione di reclocking e mi sono impantanato quando sono andato a verificare con l'oscillo che frequenze buttava fuori il mio 723 hackerato: il link postato sopra spiega che il formato Sony ha una frequenza di BCK di 2.11 MHz mentre per l'IIS abbiamo 2.8 MHz.

Ebbene ho temuto che il mio hacker avesse problemi, visto che la frequenza, anche impostando IIS, non cambiava dai multipli di 2.11 MHz. (a seconda del fattore di sovracampionamento)

Oggi ho fatto un po' di ricerche e in una nota è detto che la conversione di formato funziona solo col volume al massimo. Stasera verifico, ma ciò vuol dire che per i telecomandi dei nostri ampli dovremo usare una decodifica non RC5 (almeno per il volume)

Ciao

Andrea

Inviato: 26 ott 2006, 14:41

da andypairo

Piccolo update: ho provato ma a prescindere dal volume ottengo sempre frequenze "Sony".

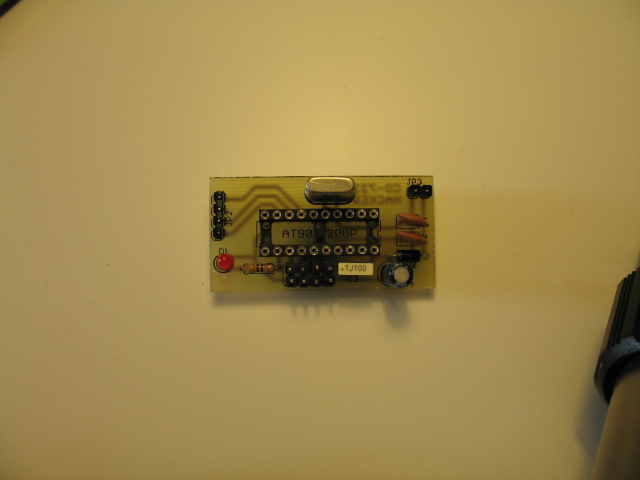

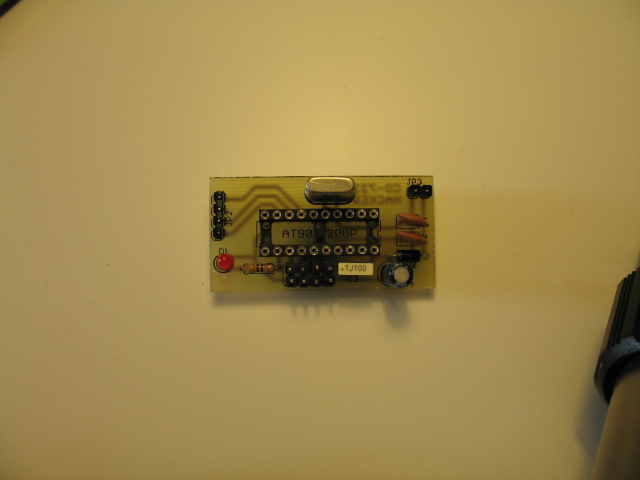

Io uso l'Atmel AT90S1200 a 4 MHz, proverò con un AT90S2313 e eventualmente cerco di minimizzare la lunghezza dei collegamenti per vedere se la cosa migliora.

Marco, visto che hai un chip, prova per favore se a te funziona.

Ciao

Andrea

Inviato: 26 ott 2006, 16:34

da PPoli

...paolo: visto che hai la CDPRO...

Magari l'avessi la CDPRO, avevo solamente valutato l'idea di comprarne una.

Inviato: 27 ott 2006, 00:42

da titano

Marco, visto che hai un chip, prova per favore se a te funziona.

Non l'ho ancora montato a dire il vero.

Se ti va ti mando lo stampato che avevo preparato cosi lo provi tu. Va saldato direttamente alla pcb frontale.

[

Anche perchè l'oscilloscopio che usavo prima di traferirmi l'avevo solo in prestito e quando ho cambiato casa l'ho riconsegnato al suo padrone...non saprei come fare la misura al momento.

Tu come l'hai testato a proposito? Mi pare che il circuito funzioni solo quando parte la lettura. Giusto?

Marco

Inviato: 27 ott 2006, 03:11

da andypairo

Aggiornamento: ho costruito un secondo hacker e l'ho montato sul secondo CD723 in mio possesso... stesso risultato!

Non mi spiego allora come sia possibile che il francese ci sia riuscito....

http://belinfabien.free.fr/cd/cd723/cd723.htm a meno che in Francia i CD723 usino un firmware diverso... gli ho mandato una mail, vediamo se risponde....

Speriamo in bene..

Ciao

Andrea

Inviato: 27 ott 2006, 14:12

da andypairo

Ecco la risposta di Fabien:

Hi Andrea,

The hacker worked perfectly for me, exept when you change the volume with the cd723 remote control. You have to let it at max (20) and block it by pressing edit two seconds.

For the clock frequency, 2.11mhz bck is ok and correspond to no oversampling.

Difference between i2s and eiaj (original format) is not a bitclock frequency, but in bit order and shifting of one bit of the left/right clock and bit clock.

You can't see it by measuring the frequency, maybe you can with a good scope.

At least is the oversampling rate changing works, no reason for i2s/eiaj to don't.

Good luck in your modification, it's worth the trouble !

regards,

Fabien

Quindi sembrerebbe che la cosa sia possibile, ma voglio verificare (ho sempre visto 2,8MHz come frequenza IIS). Proverò attaccando un TDA1543 e vediamo cosa esce.

Ciao

Andrea

Inviato: 27 ott 2006, 15:25

da Davide

Salve a tutti,

mi intrometto nella discussione poichè credo di poter dare qualche utile chiarimento.

I due protocolli standard per bus seriale I2S ed EJAI definiscono di fatto

la struttura dati delle linee DATA e WCK e le relative commutazioni ma non pongono vincoli particolari sulla lunghezza della parola digitale o sulla frequenza del bit clock BCK.

Sta di fatto comunque che in tutte le macchine di derivazione Sony e standard EJAI il datastream primario (non oversampling) ha sempre

un BCK a 2.11 MHz e WCK=BCK/48 quindi la max lunghezza di parola (DATA) è 48 bit (per canale).

In tutte le macchine di derivazione Philips I2S il datastream ha in genere:

BCK=2.82 MHz e WCK=BCK/64 quindi con max lunghezza di parola di 64 bit.

Nelle macchine "ibride" in cui c'è la necessità di intefacciare chipset che adottano formati diversi la conversione viene fatta introducendo opportuni ritardi sulle linee DATA e WCK generalmente utilizzando qualche flip-flop o registro.

Risulta invece piuttosto difficile - nonchè praticamente inutile - modificare la frequenza del BCK che quindi viene mantenuta come nello standard sorgente.

Quindi si potrà avere, come nell' esempio in questione, un bus codificato I2S ma con BCK=2,11 MHz e lunghezza max di parola 48 bit.

La cosa non crea problemi al chip che riceve il bus convertito I2S anche perchè la frequenza di clock è anche più bassa!

Quello che conta veramente è che la frequenza di WCK sia la stessa perchè WCK determina la frequenza di campionamento e quindi il latch del convertitore DA.

Infatti in entrambi i casi si ha:

2,11MHz/48= 44,1KHz

2,82MHz/64= 44,1KHz

In sostanza l'accrocco...dovrebbe funzionare....

Spero di aver chiarito qualche dubbio.

Ciao

Davide

Inviato: 27 ott 2006, 16:40

da andypairo

Ciao Davide,

il tuo intervento è certamente gradito e utile, come lo sono eventuali considerazioni relative al progetto in studio che ti invito a fare

.

In ogni caso verificherò "ad orecchio" se il formato è a posto.

La buona notizia è che un BCK a 2.11 MHz permette una efficace strategia di reclocking e sincronizzazione della meccanica a partire dalla frequenza standard impiegata di 8.4 MHz senza dover ricorrere ad accrocchi strani

Ciao

Andrea

Inviato: 27 ott 2006, 17:29

da Davide

Ciao Davide,

il tuo intervento è certamente gradito e utile, come lo sono eventuali considerazioni relative al progetto in studio che ti invito a fare

.

In ogni caso verificherò "ad orecchio" se il formato è a posto.

La buona notizia è che un BCK a 2.11 MHz permette una efficace strategia di reclocking e sincronizzazione della meccanica a partire dalla frequenza standard impiegata di 8.4 MHz senza dover ricorrere ad accrocchi strani

Ciao

Andrea

Originally posted by andypairo - 27/10/2006 : 11:40:50

Ciao Andrea,

una considerazione importante da fare quando si parla di reclocking è che il circuito deve essere progettato e realizzato con estrema attenzione.

Il reclocking sincrono (perchè è di questo che parliamo immagino) può essere un ottimo sistema per ridurre il jitter associato a bus "rumorosi".

Tuttavia va fatto con cognizione di causa altrimenti può diventare esso stesso la sorgente principale di Jitter.

Bisogna conoscere accuratamente le relazioni temporali fra i segnali del bus ed il Clock reference con il quale si vogniono sincronizzare, considerando attentamente i ritardi introdotti dai percorsi di segnale (linee di trasmissione) e soprattutto i parametri temporali di commutazione delle porte logiche utilizzate per il reclocking... poi bisogna utilizzare ovviamente le stesse porte previste dal progetto!!

Molti dei circuiti di reclocking che si vedono in giro sembrano non considerare questi fattori fondamentali, ed assomigliano di più a dei generatori che a dei riduttori di jitter.

Non ho ora il tempo ed il modo di verificare attentamente i circuiti di reclocking adottati nei link che hai proposto, quindi non so dirti a quale "categoria" appartengano.

Mi conforta però il fatto che queste problematiche sembra siano satte considerate dagli autori e che dietro sembra esserci un studio serio dei circuiti proposti (verifiche strumentali comprese!), questo depone a loro favore...

Ciao.

Davide

Inviato: 28 ott 2006, 02:35

da andypairo

Nuovo aggiornamento: ho provato il tutto "ad orecchio" e in effetti in modalità IIS col TDA1545A si sente quasi esclusivamente rumore e, a tratti qualcosa che ricorda la musica, per cui il cambio di formato direi che c'è.

Riprendo allora il discorso abortito per i dubbi esposti pochi post sopra: il reclocking.

Parte 1 - reclock

Lo schema di base riprende quello presente sul sito di Peufeu, visto che sia il TDA1541A che il TDA1545 campionano il dato sul fronte di salita del BCK successivo al cambio di stato di WS: gli adattamenti sono semplicemente di piedinatura.

Frequenza del master clock: il quarzo montato sul CD723 è da 8,4x MHz ma occorre fare alcune considerazioni:

- è sufficiente che la frequenza di reclock sia un multiplo del BCK (2,1MHz * fattore sovracampionamento), quindi se vogliamo sfruttare tutte le possibilità offerte dal lettore (max 4x OS ) ci serve un multiplo di 8.4x MHz

- bisogna generare una frequenza idonea per il DEM reclocking, compresa tra 4xfs (176 kHz) e 8xfs(384 kHz)

-il filtro digitale usa un PLL per ricavare una frequenza multipla di 8.4 Mhz per lavorare ed esiste la possibilità di usare un clock a 33.2 MHz disattivando il PLL interno. Sicuramente senza reclock ci sarebbe un vantaggio ma visto che riclocchiamo i dati non credo si abbiano grossi vantaggi

In sostanza per ridurre al minimo le frequenze in gioco e semplificare la circuiteria (divisori per ricavare il DEM reclock) io opterei per stare sugli 8.4 MHz.

Dividendo questa frequenza con un contatore sincrono per 32 otteniamo un DEM reclock a 264 kHz (6xfs)

Il tutto è possibile perchè usando l'hacker non c'è cambio di bitrate ma solo di formato dati (nei DAC con formato dati Philips solitamente il BCK è di 2,8Mhz) e quindi un clock unico fa sia da "master clock" per la conversione che da clock di sistema.

Per una descrizione sul principio del reclock adottato e per la motivazione delle scelte vi rimando al sito di Peufeu, non sarei in grado di spiegarlo meglio.

Per oggi basta... ogni commento è ben accetto.

Ciao

Andrea

Inviato: 29 ott 2006, 16:59

da andypairo

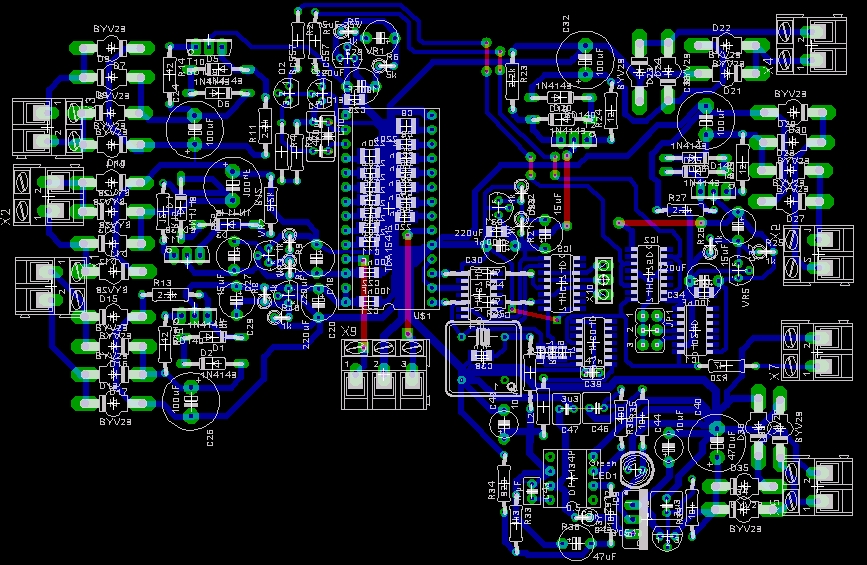

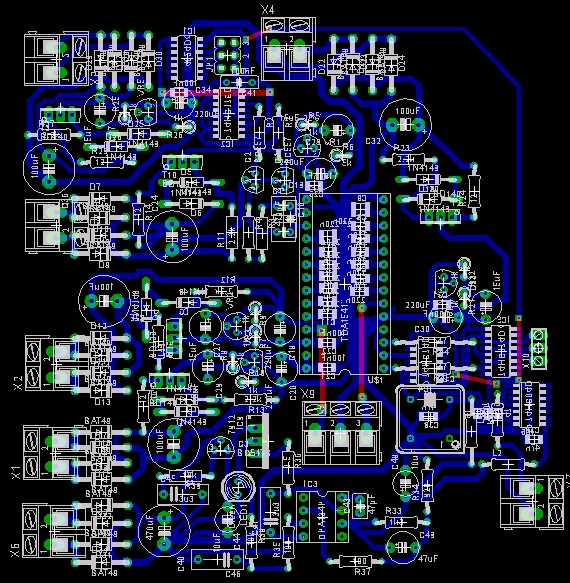

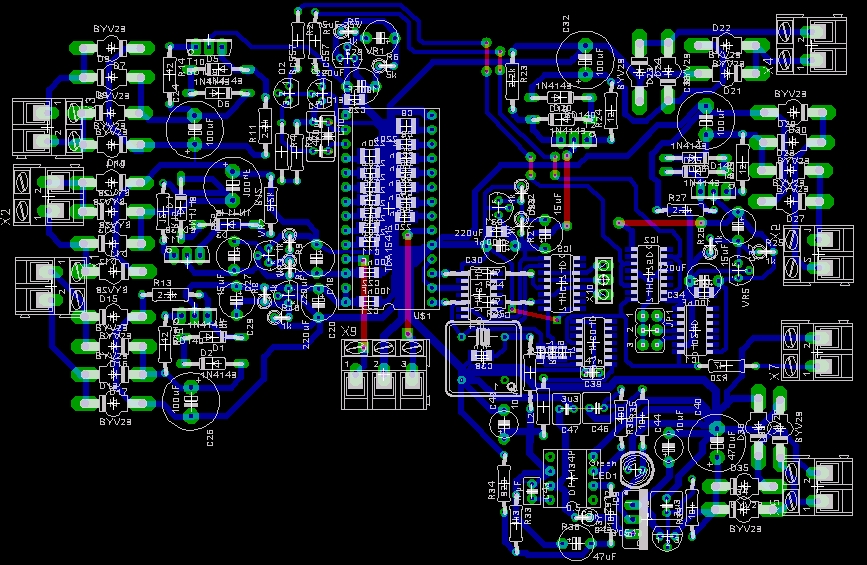

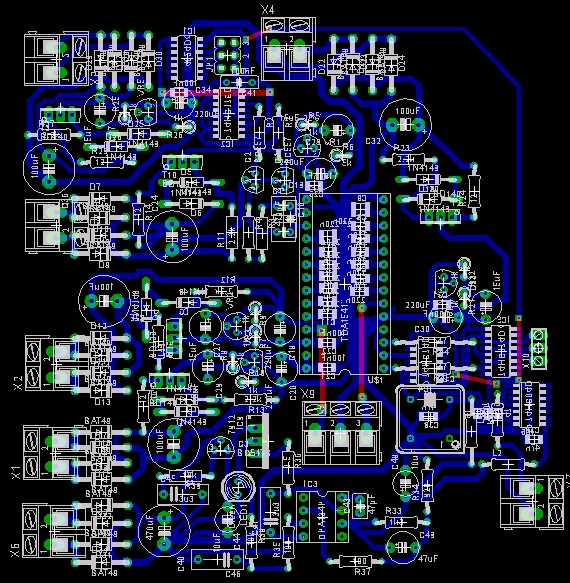

Nel file zippato trovate la prima implementazione delle sezioni di reclock.

Commenti ben accetti, possibilmente non a lavoro già fatto

.

Ciao

Andrea

Allegato: Reclock.zip ( 25028bytes )

Allegato: Reclock.zip ( 25028bytes )

Inviato: 02 nov 2006, 06:14

da PPoli

Inviato: 02 nov 2006, 21:16

da andypairo

Pur non avendolo mai visto direi che abbiamo pensato a soluzioni simili.... diciamo che le varie tipologie sono note, occorre metterle assieme in modo adeguato....

Una domanda a Marco (o a chi intende partecipare) sulle alimentazioni: d'accordo i regolatori separati per le varie sezioni (+5 -5 e -15 TDA, Clock, porte reclock e dem reclock, stadio di uscita...), conviene anche separare i secondari?

Io seguirei l'approccio "alla Pedja" (per il cui DAC ho organizzato un gruppo d'acquisto presso la Tector), ma un trafo custom del genere costò circa 40-45€ , in pratica quanto ho pagato il CD723.

E' vero che era un tantino sovradimensionato (1A per secondario)...ma non credo che si possa scendere sotto i 25-30 anche dimezzando le correnti.

Gradirei pareri in merito.

Inoltre in uno scambio di email ho sentito dire miracoli della separazione delle alimentazioni delle varie sezioni della meccanica... attendo dettagli prima di approfondire!

Ciao

Andrea

Inviato: 02 nov 2006, 21:30

da plovati

Prova a darmi le specifiche del trafo che vorresti, abbiamo un poco di cose in ballo e spero che il trasformatorista ci tratti meglio portandogli un pacchetto di lavoro più consistente.

_________

Piergiorgio

Inviato: 02 nov 2006, 22:18

da andypairo

Ciao,

diciamo che è ancora un po' presto per avere delle specifiche precise.

Il trafo per il DAC di Pedja aveva:

- 5 secondari da 8V - 1A

-2 secondari da 17V - 1A

-1 secondario da 22V - 1A

-due secondari da 80V 50 mA (anche se poi ne hanno dimenticato uno)

-un secondario 6,3V 1,5 A

Era un toroidale incapsulato, il secondario dimenticato è stato "barattato" con la resinatura.

Ciao

Andrea

Inviato: 02 nov 2006, 22:44

da titano

Io credo che l'ideale sarebbe separare i trasformatori.

Uno per gli stadi "digitali" (raggruppando dac, SAA7XXXX ed eventualemnte il clock), uno per gli stadi analogici e uno per servo e motori.

Motore e servo funzionano con basse correnti "nominali", con spunti di corrente piuttosto elevati. Meglio sperare galvanicamente dalle altre alimentazioni questi rami.

Gli stadi digitali sono "rumorosi" e separarli il più possibile dalle altre alimentazioni pare essere il modo migliore di evitare di inquinare il resto.

Mi baso su alcuni scambi di missive con Thorsten Leasch. Tra l'altro secondo lui separare il master clock e alimentarlo con una alimentazione dedicata a basso "leakege" era secondo lui l'unico modo per limitare fortemente l'introduzione di jittler eccessivo (invece di limitarlo...)

Nessuno di questi trasformatori in realtà ha bisogno di essere molto "grande" (leggi VA) quindi volendo si potrebbe far stare 3/4 piccoli trasformatori anche commerciali nella zona a dx del lettore, ripensando completamente le pcb interne.

Tutto questo sempre che si decida per stadi di conversione I/V e buffer non a tubi. Nell'ottica di mantenere tutto nel telaio originale scarterei a priori questa soluzione.

Che ne dite?

Marco

Inviato: 02 nov 2006, 23:31

da andypairo

Per quanto riguarda motore e servo, oltre che per le logiche di funzionamento del player credo si possa riutilizzare il trafo originale, magari separando con regolatori dedicati le varie funzioni.

Per il resto vedo che siamo d'accordo sulla separazione, anche se tu mi sembri più drastico

Non credo sia così necessario, usando alimentazioni shunt caricate da CCS, separare anche i trafo.

Io poi contavo di riutilizzare uno dei trafo del GB....comunque lo scopo del mio post era di decidere se optare almeno per avere secondari separati in modo da buttare giù uno schema di massima.

Ciao

Andrea

Inviato: 07 nov 2006, 19:05

da marziom

sono lento lo so.... ma sto rileggendo piano piano il 3D e mi è venuta una domanda:

nessuno ha mai provato a bufferare il segnale proveniente da un ricevitore (es. 8412) e poi ributtarlo fuori con un clock locale stabile?

.... si eliminerebbe il probelma alla radice.

marzio

Inviato: 07 nov 2006, 21:15

da cantinaro

Ciao Davide,

il tuo intervento è certamente gradito e utile, come lo sono eventuali considerazioni relative al progetto in studio che ti invito a fare

.

In ogni caso verificherò "ad orecchio" se il formato è a posto.

La buona notizia è che un BCK a 2.11 MHz permette una efficace strategia di reclocking e sincronizzazione della meccanica a partire dalla frequenza standard impiegata di 8.4 MHz senza dover ricorrere ad accrocchi strani

Ciao

Andrea

Originally posted by andypairo - 27/10/2006 : 11:40:50

Ciao Andrea,

una considerazione importante da fare quando si parla di reclocking è che il circuito deve essere progettato e realizzato con estrema attenzione.

Il reclocking sincrono (perchè è di questo che parliamo immagino) può essere un ottimo sistema per ridurre il jitter associato a bus "rumorosi".

Tuttavia va fatto con cognizione di causa altrimenti può diventare esso stesso la sorgente principale di Jitter.

Bisogna conoscere accuratamente le relazioni temporali fra i segnali del bus ed il Clock reference con il quale si vogniono sincronizzare, considerando attentamente i ritardi introdotti dai percorsi di segnale (linee di trasmissione) e soprattutto i parametri temporali di commutazione delle porte logiche utilizzate per il reclocking... poi bisogna utilizzare ovviamente le stesse porte previste dal progetto!!

Molti dei circuiti di reclocking che si vedono in giro sembrano non considerare questi fattori fondamentali, ed assomigliano di più a dei generatori che a dei riduttori di jitter.

Non ho ora il tempo ed il modo di verificare attentamente i circuiti di reclocking adottati nei link che hai proposto, quindi non so dirti a quale "categoria" appartengano.

Mi conforta però il fatto che queste problematiche sembra siano satte considerate dagli autori e che dietro sembra esserci un studio serio dei circuiti proposti (verifiche strumentali comprese!), questo depone a loro favore...

Ciao.

Davide

Originariamente inviato da Davide - 27/10/2006 : 12:29:20

Scusate se intervengo in questo punto, ma il reclocking è un produttore di jitter, serve proprio a produrne di più.

Serve a generare un jitter con uno spettro ripetitivo per combattere quello casuale.

Il reclocking innalzando il livello del jitter uniforma lo spettro risultante con un floor noise più alto.

Se avete un'idea diversa forse è fuori strada...

marco

Inviato: 07 nov 2006, 22:27

da Davide

Scusate se intervengo in questo punto, ma il reclocking è un produttore di jitter, serve proprio a produrne di più.

Serve a generare un jitter con uno spettro ripetitivo per combattere quello casuale.

Il reclocking innalzando il livello del jitter uniforma lo spettro risultante con un floor noise più alto.

Se avete un'idea diversa forse è fuori strada...

marco

Originally posted by cantinaro - 07/11/2006 : 15:15:25

Quello di cui parli è il cosidetto reclocking asincrono, fatto cioè con un clock reference a frequenza molto più alta del system clock originale e non sincronizzato con quest'ultimo (è quello proposto dal noto giapponese, tanto per intenderci.... ) e fa più o meno quello che dici tu anche se non sono molto d'accordo sul discorso ripetitivo/casuale, ma potrebbe essere un problema di diverso.... understanding.

Il reclocking sincrono, fatto cioè con un reference system clock, se fatto come si deve può ridurre il jitter causato dalla propagazione del segnale di clock attraverso numerosi stadi del percorso del segnale numerico.

Ovviamente se non è fatto come si deve introduce un maggior livello di jitter che non è cosi "benefico" come quello introdotto dall' asynchronous reclocking! Questo purtroppo è il caso più frequente nelle soluzioni che si trovano in giro......

Ciao

Davide

Inviato: 07 nov 2006, 23:58

da mauropenasa

Giusto per capire:

Visto che è abbastanza consolidata l' opinione che un bassissimo jiitter porta semplicemente a "sonorità fredde" (intese termoionicamente parlando ovviamente), ha un senso porsi questo problema in ambienti in cui la THD e IMD finale ottenuta non si è manco in grado di analizzarla ?

Cioè, dato che qui si parla non di raggiungere traguardi prestazionali ma solo sonici, qualcuno si è posto il problema di cosa faccia o non faccia alle proprie orecchie il jiitter, ed in particolare se queste configurazioni con TDA1541 risente in modo particolare di questo problema ?

Personalmente credo che questo sia semplicemente un "non problema", nel senso che "sonicamente" ho sentito molti più dac collegati in spdif (ottico o coax) "suonare bene" che questi famigerati sistemi "jiitter free".....

Qualche maligno potrebbe far notare che nella maggior parte dei sistemi di demodulazione analogica usati per il TDA, ma anche nel TDA stesso esistono dinamiche distorsive spesso maggiori anche di un ordine di grandezza rispetto a quelle del jiitter.

Poi sulla reale entità di questo fenomeno (jiitter) ci sarebbe molto da considerare. Ne sento parlare come se fosse una cosa che "gira sul tavolino" di tutti.

Singolare che ci siano migliaia di diys che non dormono la notte a causa di questo "presunto" problema (sempre inferiore a -80dB anche in casi limite), mentre di avere stadi I/V o amplificatori con il 3% di THD (-30dB !!) fa solo colore....

ciao

Mauro

http://www.webalice.it/mauro.penasa/index.html

Inviato: 08 nov 2006, 03:26

da andypairo

Dunque....

marzio: un reclocking come lo descrivi tu non è fattibile perchè due clock, anche fossero della stessa frequenza nominale, non sarebbero mai uguali e avresti una fase relativa che cambia, fino al punto di avere perdita di dati (quando il ritardo supera una certa soglia). Occorre mantenere il sincronismo tra i due, e lo si può fare "passando" il clock alla meccanica oppure usando un VCO sempre sulla meccanica come viene fatto se non erro nel Tent Link.

marco (cantinaro) : ti ha già risposto Davide

mauro: il tuo discorso è un tantino disfattista, nel senso che nessuno di noi ha la pretesa di essere un guru per cui, ben consci dei nostri limiti, cerchiamo di imparare qualcosa magari solo mettendo in pratica (con un poco di "granu salis") ciò che ci sembra maggiormente valido tra le proposte che vediamo in giro.

Non so quanti abbiano a disposizione la strumentazione per poter fare valutazioni del genere, per cui ci dovremo basare su buon senso e sull'esperienza (altrui e propria).

In ogni caso le "dinamiche distorsive" interne al TDA le sto prendendo in considerazione (mi riferisco al condizionamento dei segnali IIS per ridurre le interferenze sul substrato) ma onestamente fare un discorso di soli numeri su jitter e distorsioni sai bene che non è corretto, soprattutto dal punto di vista tecnico/scientifico che contraddistingue solitamente i tuoi interventi.

Nessuna polemica, spero però in interventi più costruttivi...

Ciao

Andrea

Inviato: 08 nov 2006, 15:51

da mauropenasa

mauro: il tuo discorso è un tantino disfattista, nel senso che nessuno di noi ha la pretesa di essere un guru per cui, ben consci dei nostri limiti, cerchiamo di imparare qualcosa magari solo mettendo in pratica (con un poco di "granu salis") ciò che ci sembra maggiormente valido tra le proposte che vediamo in giro.

Non so quanti abbiano a disposizione la strumentazione per poter fare valutazioni del genere, per cui ci dovremo basare su buon senso e sull'esperienza (altrui e propria).

In ogni caso le "dinamiche distorsive" interne al TDA le sto prendendo in considerazione (mi riferisco al condizionamento dei segnali IIS per ridurre le interferenze sul substrato) ma onestamente fare un discorso di soli numeri su jitter e distorsioni sai bene che non è corretto, soprattutto dal punto di vista tecnico/scientifico che contraddistingue solitamente i tuoi interventi.

Nessuna polemica, spero però in interventi più costruttivi...

Mi dispiace che tu lo viva come "disfattista".

Sicuramente è colpa del modo in cui pongo le questioni, ma questo vale per molti argomenti, come nel "caso preconcetto"....

Ovviamente tutti sono liberi di giocare con soluzioni inventate a tavolino dai loro colleghi autocostruttori, cosi come porsi problemi inventati ad arte dai grossi nomi audio per giustificare i costi dei loro apparecchi.....

Se volete posso "rispondere a gettone" dicendo di credere fermamente a tutti gli argomenti ed inventandomi di volta in volta elementi teorici a conferma di esse (come fanno quelli a pagamento sulle riviste)..... :p

Non preoccuparti, non metto giù polemiche gratuite....; )

ciao

Mauro

http://www.webalice.it/mauro.penasa/index.html

Inviato: 11 nov 2006, 14:33

da andypairo

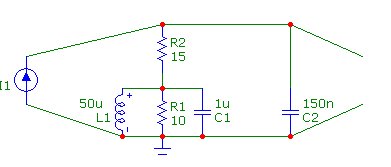

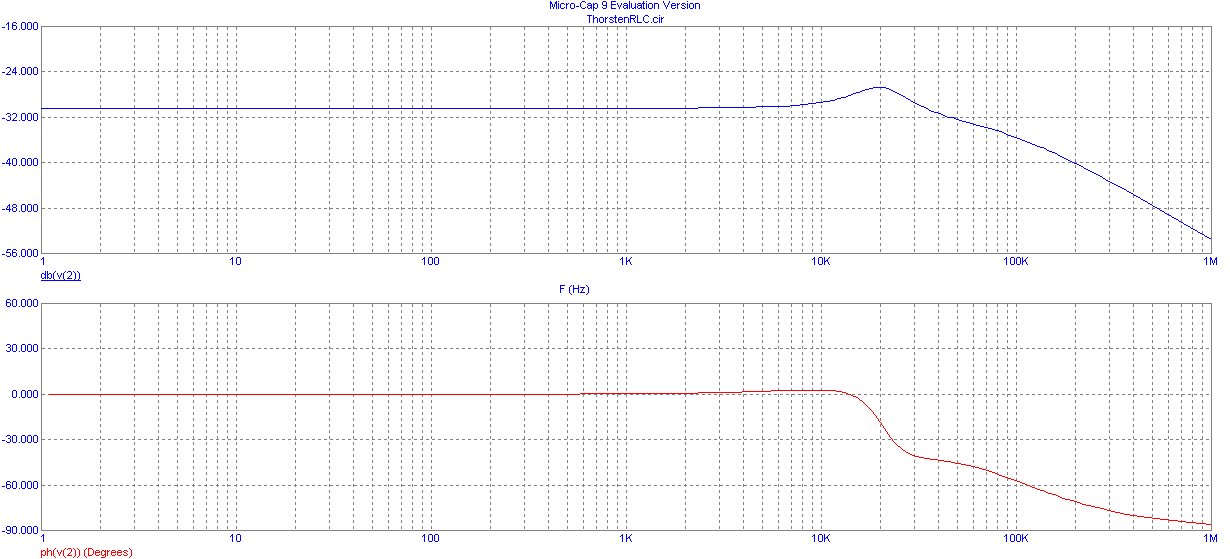

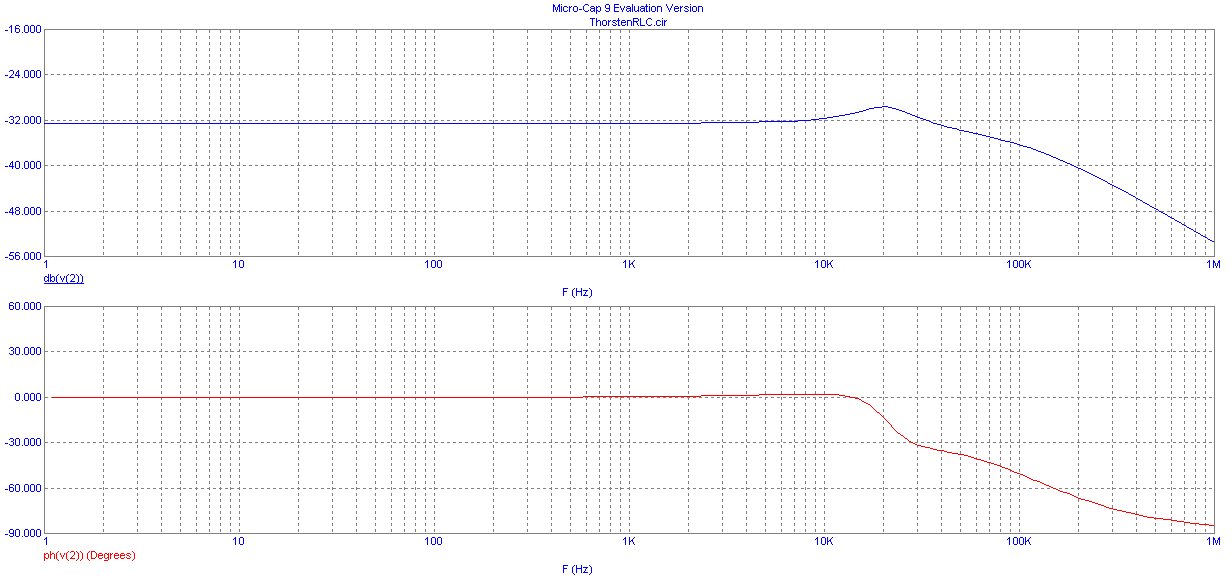

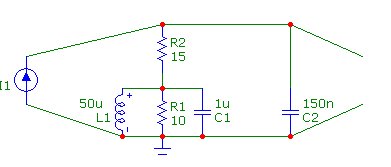

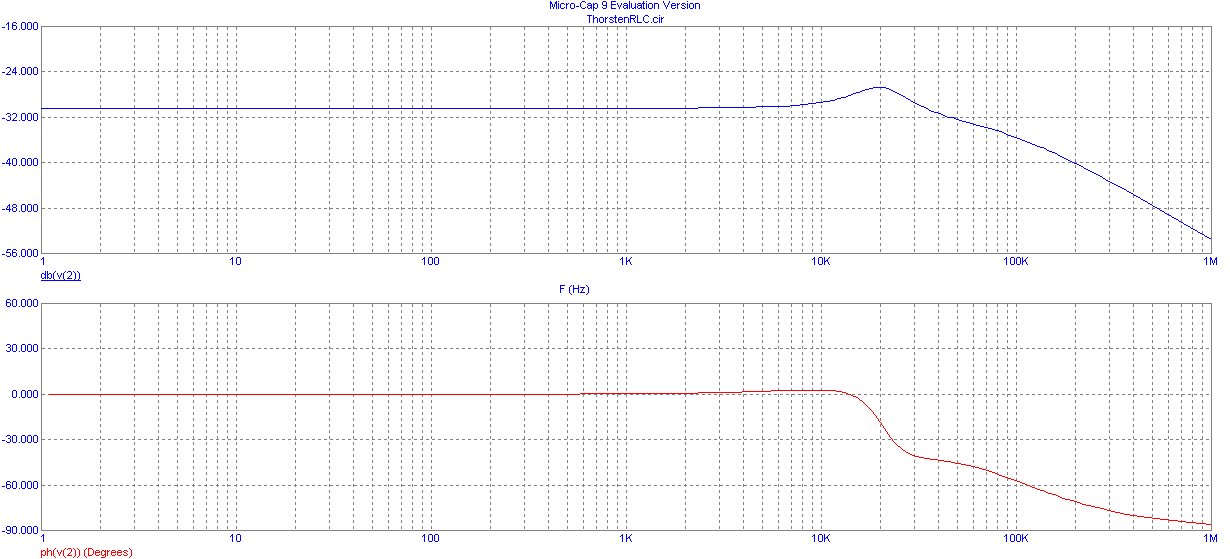

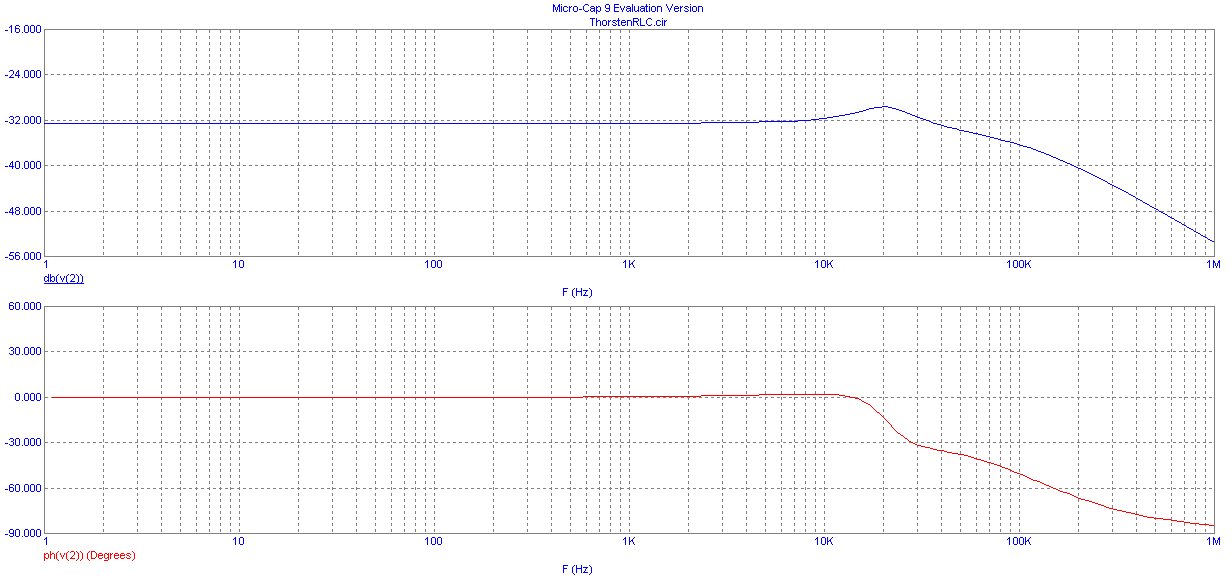

Piccolo aggiornamento: ecco lo schema di base delle sezioni di reclock.

Per ora sono utilizzati regolatori shunt per tutto (valori da verificare).

Potrebbe essere il caso di passare a regolatori differenti per le logiche digitali (mi viene in mente un regolatore low-noise della Linear che era consigliato per l'XO Tent)

Infine uno studio più approfondito sul DEM reclock ha rivelato che sono stati presentati 3 circuiti differenti, quello di HtP, uno che non inverte il segnale verso il pin 17 e uno che omette i PNP e entra solo sul pin 16 lasciando sconnesso il 17.

Di quest'ultimo ho ricevuto conferma da gente che l'ha costruito riguardo al funzionamento, per cui potrebbe essere il caso di passare a questo schema (che consente una certa semplificazione tra l'altro)

Sto studiando un'altro po' di info su come realizzare i decoupling, cosa non banale per via della costruzione del chip.

Per quanto riguarda il condizionamento dei segnali IIS:

- HtP citava che lo swing necessario di tensione, essendo le logiche a commutazione di corrente - current routing- è di circa +/-200 mV intorno a 1,3V e inoltre per diminuire le interferenze sul substrato sarebbe bene limitare lo slew rate dei segnali

- non ci sono stati riscontri unanimi sui miglioramenti ottenibili in questo modo (al massimo "subtle improvement"), se non un caso citato su una rivista in cui l'autore, condizionando i segnali ripulendoli dagli overshoot legati alla cattiva progettazione degli stadi a monte aveva ottenuto un drastico miglioramento.

Viste le due cose credo sia possibile eliminare parte dei problemi usando logiche a 3.3V (e 5V tolerant in ingresso) per il reclock dei segnali IIS. Il "problema" è che la serie LVX c'è solo SMD, ma credo che forse era già in preventivo l'uso di tali componenti.

Ciao

Andrea

Allegato: Reclock-Dem01.pdf ( 96289bytes )

Allegato: Reclock-Dem01.pdf ( 96289bytes )

Inviato: 22 nov 2006, 17:35

da andypairo

In attesa di commenti sul circuito postato verificherei le possibilità per le alimentazioni:

-Shunt con TL431 pilotato da CCS

-Alim. discreto "open loop" come usato da Pedja per le alimentazioni del TDA

-Regolatori low noise?

Ciao

Andrea

Inviato: 22 nov 2006, 18:32

da gluca

Il Ciuffoli non ha gradito i TL341 (ma con R ... no CCS) anche se non posta misure particolari in merito.

http://www.audiodesignguide.com/DAC_final/DacFinal.html

Ciao

Gianluca

PS seguo il thread nella mia oscura "innioranza" per il futuro

---------> DISCLAIMER: ooops credo di aver detto una fesseria ... scusate <---------

Inviato: 22 nov 2006, 18:49

da titano

Mah, più che un "problema" legato al ccs mi pare che Ciuffoli abbia trascurato troppo le tecniche di bypass necessarie a far funzionare bene il Tl431.

Per molti pare essere una buona soluzione principalmente sulle alimentazioni "digitali" con in uscita quella che Thorsten chiamava "triplette": un sanyo oscon e due ceramici (un Y7R ed un Y5U) che a quanto pare sono, insieme, un bypass ottimale per le non linearità del TL.

Lettura interessante...

http://www.tnt-audio.com/clinica/regula ... ance2.html

Marco

Inviato: 22 nov 2006, 19:12

da gluca

Si, si ... conoscevo quell'articolo di TNT. Molto interessante ed infatti userò i TL in futuro.

Però riuscire a sentire ad orecchio la differenza che fa un condensatore in più su un TL341 che alimenta un chippino... non lo so, io non ci riesco o cmq non ho la pazienza di fare prove e riprove. OH! poi con tutti quei cablaggi volanti del Ciuffoli l'efficienza dei bypass forse viene anche persa.

Ciao

Gianluca

---------> DISCLAIMER: ooops credo di aver detto una fesseria ... scusate <---------

Inviato: 22 nov 2006, 20:49

da andypairo

Dunque, in vari thread sparsi tra diyaudio (

http://www.diyaudio.com/forums/showthre ... genumber=1) e diyhifi (

http://www.diyhifi.org/forums/viewtopic ... c&start=60) sono state sottolineate alcune cose:

-15V : solo analogico

+5V: analogico e digitale

-5V: analogico e digitale

-i generatori di corrente per il DEM matching sono molto sensibili alla stabilità tra -5 e -15V (e c'è chi suggerisce di fare come nel Marantz CD7 che ricava il -5 dal -15, comunque un decoupling come minimo ci va)

-le correnti analogiche di segnale circolano tra i pin di uscita e i +5V (che quindi dovrebbe trarre benefici da un'alimentazione "shunt", secondo quanto citato nei post 81 e 87 di diyhifi)

E' un po' un casino ma credo si possa venirne a capo.

Ciao

Andrea

Inviato: 23 nov 2006, 05:41

da andypairo

Per evitare confusione dovuta ad una traduzione magari non impeccabile quoto direttamente dai thread:

..............

Again: all supply pins are not just analog or digital, they are both:

+5 digital and mirrored output currents (going to -15)

-5 digital and current ref generator

-15 current ref generator and return pin for the output currents (incl those

on +5)

digital currents are mostly between +5 and -5, less between +5 and dgnd.

Not shure if there is a lot going on at agnd, no audio signals anyway.

...................

now keep the 10V as constant as you can: decouple -15 directly to -5

so: -15 to gnd, -5 to gnd, +5 to gnd, but also -15 to -5

..................

digital part: all logic is current mode (constant current).

most of the supply +5 to -5, lesser part +5 to dgnd.

Capacitive spike to -15V.

analog part: -15: current reference generator, dem oscillator and

ring-counter. Not to agnd, but to -5.

This 10V should be as constant as possible.

Decouple all supply pins and DEM caps to agnd.

....................

And now the fun/final part: the output (at unexpected places):

The dac is can be seen as a digital controlled differential pair with a bias current of 2mA and a current swing of 4mApp. One output is the dac output, the other flowing into the +5V.

So a DC current of 2mA into the outputs and 4mA into +5 (2*2), coming out at -15 pin (2+2+4=8mA).

'Audio' currents (-2 to 2mA) from output to +5.

Swing at the output pins therefore 0 to 4mA.

Therefore there are no signal currents in agnd

The voltage of the output pins should be kept at agnd level.

So with resistor i/v the current will go:

output pin - resistor - agnd - decoupling cap - +5 supply pin...

Changing the decoupling cap has directly impact on the sound.

Options to close the loop better (to actually know where the currents are):

- opamp i/v with +supply of the opamp same as +5V of the dac.

- differential setup, one dac per channel (my setup, i was

lucky ): current into +5: [2+2+(-audio+(audio)] = 4mA = dc.

- resistor i/v: sense the voltage, convert to current and feed to +5.

- resistor i/v and shuntreg for the +5 supply.

current: output pin - resistor - agnd - shuntreg - +5 supply.

- avoid a series regulator for the +5. Part of the current will use the

decoupling cap, part the series reg.

Che ne pensate?

Da quel che si legge si evince che:

-Se usiamo un I/V passivo (resistenza) l'alimentazione a +5V è meglio che sia shunt, le altre è bene che siano ben stabili (soprattutto i 10V tra -5 e -15)

-Il disaccoppiamento va fatto tra le alimentazioni e gnd ma anche tra -5 e -15

Altre idee?

Ciao

Andrea

Inviato: 25 nov 2006, 03:02

da andypairo

Proseguendo nel mio soliloquio

ho colto l'occasione di una richiesta di montaggio di un dac conto terzi per vedere le scelte adottate da Pedja per il suo ultimo lavoro, l' AYA DAC.

In questo progetto fa largo uso di regolatori discreti open loop, in sostanza abbiamo uno zener pilotato da CCS che, adeguatamente filtrato, va sulla base di un darlington.

Le uniche eccezioni sono dei regolatori shunt per i flip/flop del reclocker e per gli AD844 di uscita.

E' da notare come anche nel circuito diy dell'XO tent sia suggerito un circuito simile (anche se più semplice).

Per quanto riguarda i condensatori di decoupling del DEM (valori di qualche decimo di uF, più grande per il MSB) dobbiamo scegliere quale compromesso adottare: siccome servono condensatori di qualità (basso-bassissimo leakage) l'idele sarebbero dei MKP, che però sono ingombranti e non consentono un layout compatto.

Il solito Pedja è passato per questo motivo ai Black Gate NX che sono piuttosto compatti e dovrebbero essere qualitativamente adeguati.

L'alternativa è cercare dei MKP (ma esistono anche altri dielettrici) in SMD e verificare se si riesce a trovarne di sufficientemente piccoli. Se si trovano magari si riesce a infilarli direttamente sotto il chip, a tutto vantaggio della loro efficacia. Inoltre i componenti SMD non hanno l'induttanza parassita dei reofori.

Chi si offre di trovare una soluzione?

Ciao

Andrea

Inviato: 25 nov 2006, 15:55

da titano

Chi si offre di trovare una soluzione?

Arcotronics R82. Guarda il valore di induttanza propria...

Attachment: r82.pdf ( 58042bytes )

Attachment: r82.pdf ( 58042bytes )

Marco

Inviato: 25 nov 2006, 16:10

da mauropenasa

Andrea, devi decidere cosa ti serva realmente, in termini di caps di bypass.

Se il problema è il leakage, ti servono caps con elevato coefficiente dielettrico, quindi i migliori sono i ceramici multistrato, che hanno un coefficiente dielettrico di almeno una grandezza maggiore dei migliori MKP.

Se il problema è la stabilità termica e capacitiva in tutte le condizioni, e se il valore capacitivo supera i 1000pF circa (limite per le versioni C0G o NP0 ceramiche), allora ti serve ripiegare sugli MKT come quelli citati da Marco oppure qualche versione miniatura di MKP o KP.

Non so quanto i black gate, a parte il nome altisonante, siano superiori a qualsiasi altra soluzione, sia essa a ceramici (comunque sempre superiore a qualsiasi altra soluzione se si tratta di filtrare alta frequenza senza tanti preamboli) che R82 o simili.

Per il resto basta ricordarsi che più sono piccoli di dimensione, i caps, (e corti i reofori) minore sarà la ESL, quindi più efficienti in generale.

Insomma, l' importante è conoscere il problema da risolvere....

ciao

Mauro

http://www.webalice.it/mauro.penasa/index.html

Inviato: 25 nov 2006, 19:00

da riccardo

Posso portare un contributo molto imho, ricavato dalla osservazione, dall'ascolto, e da confronti

Vi riassumo la questione:

per prima cosa, un confronto tecnico fra il miglior cd marantz q/p che è il marantz CD40, e il loro migliore Audiophile oriented, sempre per Q/P, il marantz cd94MKII.

Nel caso della piccola macchina, il cd40, marantz negli impieghi di bypass ha usato ceramici multistrato SMD, "on pin".

Il cd94 monta nelle stesse situazioni, R82 Arcotronics con piste da cui è ricavabile ESL e ESR aggiunte al condensatore (non da me, ma se po' fa).

Al vertice, faccio notare, esiste il marantz cd 7, che con altre esigenze e differente arcihitettura, secondo me meramente equalizzante, usa Panasonic Sb (quelli amaranto) con piste lunghe uno sproposito e una notevole circonvoluzione (cmq, suona bene, mi dicono).

Dai miei confronti emerge quanto segue, fra le due prime macchine: montando su cd40 ben restaurato (vedi mio 3d), un dac S2, il confronto con il CD94 MKII ceh monta una coppia di S1 si fa per niente affatto improbabile.

Ovviamente il cd94 mostra doti timbriche in assoluto migliori, ma il divario in termini generali non rappresenta la differenza di prezzo originale tra le due macchine.

Questo, tradotto in buonsensese, il mio, mi fa dire che il progetto di base e le implementazioni adottate nel piccolo 40 sono valide per molte lunghezze, anche di fronte a una meccanica CDM1 e due S1.

Dal che desumerei che le indicazioni di Mauro sono, a livello soggettivo, oltre che tecnico corrette.

ah, siccome le orecchie sono le mie, nulla vi vieta di provare.

Andrea, devi decidere cosa ti serva realmente, in termini di caps di bypass.

Se il problema è il leakage, ti servono caps con elevato coefficiente dielettrico, quindi i migliori sono i ceramici multistrato, che hanno un coefficiente dielettrico di almeno una grandezza maggiore dei migliori MKP.

Se il problema è la stabilità termica e capacitiva in tutte le condizioni, e se il valore capacitivo supera i 1000pF circa (limite per le versioni C0G o NP0 ceramiche), allora ti serve ripiegare sugli MKT come quelli citati da Marco oppure qualche versione miniatura di MKP o KP.

Non so quanto i black gate, a parte il nome altisonante, siano superiori a qualsiasi altra soluzione, sia essa a ceramici (comunque sempre superiore a qualsiasi altra soluzione se si tratta di filtrare alta frequenza senza tanti preamboli) che R82 o simili.

Per il resto basta ricordarsi che più sono piccoli di dimensione, i caps, (e corti i reofori) minore sarà la ESL, quindi più efficienti in generale.

Insomma, l' importante è conoscere il problema da risolvere....

ciao

Mauro

http://www.webalice.it/mauro.penasa/index.html

Originariamente inviato da mauropenasa - 25/11/2006 : 10:10:49

Saluti

R.R.

Inviato: 26 nov 2006, 03:14

da andypairo

Dunque,

in effetti il leakage non è l'unico fattore di scelta, la stabilità del componente (temperatura e altro) è altrettanto importante.

Quindi mi orienterei su un cap a film in SMD per avere caratteristiche adeguate e possibilità di ottimizzazione del layout.

Gli R82 sono sicuramente un'alternativa più che valida ma credo che uno 0.1 uF in case 1210 (3,5 per 2,5 mm) possa permettere un layout decisamente buono.

Esempi tratti dal catalogo Mouser sono i CDE serie FCP e gli AVX serie CB

http://www.cde.com/catalogs/FCP.pdf#sea ... ubilier%22

http://www.avx.com/docs/Catalogs/cb-pen.pdf

Sono OK o mi sfugge qualcosa?

Ciao

Andrea

Inviato: 26 nov 2006, 05:13

da Arge

Prova a darmi le specifiche del trafo che vorresti, abbiamo un poco di cose in ballo e spero che il trasformatorista ci tratti meglio portandogli un pacchetto di lavoro più consistente.

_________

Piergiorgio

Originariamente inviato da plovati - 02/11/2006 : 15:30:59

io dovrei farmi fare il TU del mio Geloso....cosa dici si può fare???

mi aggiungerei molto volentieri.

ciao da Giovanni

Inviato: 26 nov 2006, 16:34

da Arge

Ricapitolando....

Se ho ben capito, tutta la parte "dopo" la meccanica e in fase di riprogettazione....

Ma scusate, tanto vale farci il nostro lettore CD, mi spiego:

Adottare una meccanica di provenienza PC ( ottime, tanto che le usano molte case) e da li partire con tutta la sezione di alimentazione,controllo e conversione....

per i telai,no problem,partendo da un buon Galaxi , posso fare tutte le modifiche "standard" per arrivare ad avere un telaio pronto al montaggio dei vari componenti.

per i frontali, ci si potrebbe appoggiare direttamente alla Hifi 2000 per la loro serigrafia e lavorazione.

E' un bella proposta, certamente "ambiziosa"

ciao da Giovanni

Inviato: 26 nov 2006, 16:45

da mauropenasa

Sembrano buoni entrambi....

Ma la sezione che devono bypassare è digitale od analogica ?

Io userei i normali ceramici X7c sul digitale, magari in soluzioni multiple scalate (es: 100nF con sopra saldato un 47nF con sopra un 10nF) a formare una specie di muro (a bassissimo costo) alle frequenze digitali in gioco, e riserverei questi filmcaps per le sezioni analogiche del dac ecc.....

ciao

Mauro

http://www.webalice.it/mauro.penasa/index.html

Inviato: 26 nov 2006, 17:17

da andypairo

I segnali in questione sono analogici e servono per il matching dinamico dei generatori di corrente interni.

Per questo l'uso di filmcaps è quasi obbligato.

D'accordissomo invece sull'uso dei ceramici per il bypass delle sezioni digitali... il problema è che il DAC non ha un'alimentazione esclusivamente digitale... ma credo che sull'alimentazione non possano fare male.

Per la proposta di Giovanni: in effetti si potrebbe anche fare, a patto di trovarne una di facile reperibilità, che usi i segnali IIS, di fare la logica di controllo (vabbè ci sono dei kit...) e di farsi il case.

Non ci avevo pensato per mancanza di capacità nei lavori meccanici e perchè il 723 ha già fatte buona parte di queste cose e costa come un Galaxy

In un primo momento quindi io mi concenterei sullo sviluppo della sezione DAC e contorno, poi se i risultati saranno tali da "meritare" un case e una meccanica ad hoc perchè no ; )

Ciao

Andrea

Allegato: HtP Dem Description.pdf ( 16629bytes )

Allegato: HtP Dem Description.pdf ( 16629bytes )

Inviato: 26 nov 2006, 17:26

da riccardo

C'è da dire che a risultato circuitale acquisito, varrebbe probabilmente la pena risolvere tutte insieme le questioni di risonanze/fragilità meccanica del leggerissimo cabinet del 723.

Saluti

R.R.

Inviato: 26 nov 2006, 17:28

da Arge

Per la proposta di Giovanni: in effetti si potrebbe anche fare, a patto di trovarne una di facile reperibilità, che usi i segnali IIS, di fare la logica di controllo (vabbè ci sono dei kit...) e di farsi il case.

Non ci avevo pensato per mancanza di capacità nei lavori meccanici e perchè il 723 ha già fatte buona parte di queste cose e costa come un Galaxy

Ciao

Andrea

Originariamente inviato da andypairo - 26/11/2006 : 11:17:01

Ciao Andrea, si può fare tutto, dipende cosa si vuole ottenere e a che costo, spesso nel nostro hobby si è portati a spendere più di un prodotto finito ( a volte),ma vuoi tralasciare la soddisfazione e la goduria nel dire l' ho fatto io ?, altrimenti perchè saremmo qui?

ciao da Giovanni

Inviato: 21 dic 2006, 15:51

da andypairo

Proseguendo...

Dando per assodato l'uso di film caps in SMD per il DEM bypassing (lasciando i ceramici in tripletta per i digitali) volevo soffermarmi sulla tipologia delle alimentazioni da utilizzare:

-Per i +5 del TDA io propendo per uno shunt col TL431

-il -5 e il -15 dovrebbero utilizzare lo stesso tipo di regolatore, se non altro per mantenere il più stabile possibile la differenza (usata per i generatori di corrente). Qui possiamo rimanere sullo shunt solito o usare eventualmente un regolatore discreto open loop come da Pedja nel suo AYA DAC.

-Per l'alimentazione del Tent clock possiamo usare, se nessuno ha idee migliori, la soluzione "diy" proposta da Tent (7808 seguito da un emitter follower opportunamente settato per i 5V)

-Per i rimanenti circuiti (DEM reclock e reclock IIS) sono aperto a suggerimenti.

Ciao

Andrea

Inviato: 26 dic 2006, 19:41

da mrjam

Ciao Andy

A titolo informativo: la psu riportata da G.Tent nel suo sito non è quella del XO2/3.

Hai visto questo alimentatore per clock?

http://www.acoustica.org.uk/flea_manual.pdf

Il progetto è di Andrew L.Weeks ...a mio avviso è degno di un pensierino ; )

A breve farò qualche prova!

Buon AudioFaidate!

Ciao

Roberto

Inviato: 26 dic 2006, 23:34

da andypairo

Ad una prima scorsa il progetto sembra piuttosto interesante ed inoltre facilmente integrabile dato il numero di componenti limitato.

Ero a conoscenza che il circuito DIY di Tent non è quello commerciale (come normale che sia), ma credo si tratti comunque di una discreta base di partenza.

Il flea, però, sembra davvero avere una marcia in più, a giudicare dal fatto che è stato progettato appositamente per un XO e che ha dei "numeri" piuttosto interessanti.

Peccato che l'AD797 sia piuttosto caro....altrimenti si poteva pensare di usarlo estensivamente....

Ciao

Andrea

Inviato: 27 dic 2006, 00:42

da mrjam

Se pur caro da digikey lo paghi il giusto. Dagli un'occhiata!

Buon AudioFaidate!

Ciao

Roberto

Inviato: 27 dic 2006, 01:17

da andypairo

Anche se lo paghi il giusto 8$ e mezzo non sono pochini per un opamp (seppur eccezionale).

Pensando di adoperarlo per tutte le alimentazioni necessarie al progetto credo aumenterebbe troppo il costo, per cui mi limiterei appunto all'alimentazione del clock o, se vogliamo esagerare, alle alimentazioni del DAC (ma ho dei dubbi)

Ciao

Andrea

Inviato: 31 dic 2006, 02:40

da andypairo

Ho aggiornato lo schema (in allegato come PDF) usando il flea per l'alimentazione del clock e rimanendo con i TL431 per il resto.

Rimane una problematica per i caps di bypass del TDA1541A: io propenderei per un valore più alto dei 100nF classici, magari un 220nF.

Il problema è che i 100nF si trovano anche in case 1210 mentre i 220n solo in case 1812 e superiori. Tradotto in soldoni con i 1210 si riesce a metterli tutti dallo stesso lato del PCB mentre i 1812 sono troppo larghi per la spaziatura tra i pin e andrebbero montati alternati uno lato saldature e uno lato componenti.

In alternativa si possono usare due 100nF 1210 in piggyback e riservare un po' di spazio in più per il pin del MSB.

Marco visto che i PCB sono "roba tua" dammi il tuo parere che poi ti mando i file eagle per lo sbroglio.

Ciao

Andrea

Allegato: DEM_Reclock.pdf ( 108055bytes )

Allegato: DEM_Reclock.pdf ( 108055bytes )

Edit: spulciando su digikey ho visto che si trovano caps fino a 1uF in case 1210 ma sono di tipo "stacked" e non PPS: secondo voi sono peggiori o sono un'alternativa adatta?

Inviato: 26 feb 2007, 21:12

da andypairo

Approfittando di qualche trasferta (e relative serate in albergo...) ho portato avanti lo sbroglio della PCB.

Ho cercato di rimanere sul monofaccia (con qualche ponticello) per riservare il "top" layer al ground plane.

Accetto commenti e consigli, visto che non ho molta esperienza a riguardo. Lo schema è nel post precedente.

Ciao

Andrea

Inviato: 23 mag 2007, 15:54

da andypairo

Ho rivisto sostanzialmente lo sbroglio, cercando di mettere le connessioni di alimentazione tutte da un lato.

Non mi sembra malaccio ma sicuramente è migliorabile.

Ora, visto che il progetto è partito come collaborazione su pungolo di Marco ma che finora, a parte i contributi visibili nel thread ho portato avanti tutto io, vorrei capire se ha senso sviluppare ulteriormente il progetto in solitaria

Avrei bisogno di aiuto per l'affinamento dello sbroglio e la produzione della PCB prototipo. Io mi farei carico dei componenti e dei test.

Una volta testato il tutto con risultati soddisfacenti possiamo vedere di fare delle PCB "definitive".

Qualcuno si offre di darmi una mano?

Ciao

Andrea

Inviato: 23 mag 2007, 17:01

da titano

[quote

Ora, visto che il progetto è partito come collaborazione su pungolo di Marco ma che finora, a parte i contributi visibili nel thread ho portato avanti tutto io, vorrei capire se ha senso sviluppare ulteriormente il progetto in solitaria

Avrei bisogno di aiuto per l'affinamento dello sbroglio e la produzione della PCB prototipo. Io mi farei carico dei componenti e dei test.

[/quote]

Se hai notato il numero di post a mio nome e la produttività dimostrata negli ultimi sei mesi credo non sia difficoltoso comprendere che non si è trattato di "razziasmo", semplicemente non ho avuto modi di ritagliarmi alcuno spazio per dedicarmi al diy, in generale.

Spero di avere più tempo a giugno, ma dicevo la stessa cosa di marzo...aprile...maggio...

Per la produzione della pcb prototipo ci penso io, non dovrebbero essereci particolari problemi.

Se ho capito bene il circuito è "a posto" e resta da sistemare la pcb, giusto? Una cosa che ti domandai già tempo fa, senza per altro avere risposta, è se hai considerato le dimensioni del telaio e il posizionamento dei collegamenti che dovrai fare, oltre a distribuire i componenti al fine di semplificare lo sbroglio...

Vista la completa revisione immagino che la domanda non fosse caduta nel vuoto.

Qualcuno si offre di darmi una mano?

Guarda, senza promettere nulla spero di riuscire ad essere più attivo tra un paio di settimane...

Marco

Inviato: 28 mag 2007, 17:35

da andypairo

Se hai notato il numero di post a mio nome e la produttività dimostrata negli ultimi sei mesi credo non sia difficoltoso comprendere che non si è trattato di "razziasmo", semplicemente non ho avuto modi di ritagliarmi alcuno spazio per dedicarmi al diy, in generale.

Spero di avere più tempo a giugno, ma dicevo la stessa cosa di marzo...aprile...maggio...

Per la produzione della pcb prototipo ci penso io, non dovrebbero essereci particolari problemi.

Se ho capito bene il circuito è "a posto" e resta da sistemare la pcb, giusto? Una cosa che ti domandai già tempo fa, senza per altro avere risposta, è se hai considerato le dimensioni del telaio e il posizionamento dei collegamenti che dovrai fare, oltre a distribuire i componenti al fine di semplificare lo sbroglio...

Vista la completa revisione immagino che la domanda non fosse caduta nel vuoto.

Qualcuno si offre di darmi una mano?

Guarda, senza promettere nulla spero di riuscire ad essere più attivo tra un paio di settimane...

Marco

Originally posted by titano - 23/05/2007 : 12:01:19

Ciao, rispondo solo ora perchè nel thread non si vedeva nulla ma nel fare il "reply" ho trovato la tua risposta (che può essere successo?)

Dunque il circuito è *abbastanza* a posto, nel senso che va provato e potrebbero essere necessari dei cambiamenti, specie per quel che riguarda il DEM reclock. La disposizione ad ora non è particolarmente studiata per il 723, perchè pensavo di fare una PCB "universale" anche per altri CD player e i segnali in comune col 723 sono, a meno di rifare anche le alimentazioni e quindi di eliminare la basetta AF, le 3 linee IIS e il clock al trasporto.

Il primo passo credo sia di verificare che le cose siano a posto dal punto di vista elettrico, per poi passare a studiare l'integrabilità nel player (che comunque ha molto spazio)

Marco, non era un attacco nei tuoi confronti quanto piuttosto un piccolo "sfogo" e un tentativo di trovare altri che potessero aiutare la causa

Ti mando a breve i file eagle.

Ciao

Andrea

Inviato: 02 giu 2007, 18:19

da STEBIL

Buongiorno a tutti , questo è il mio primo messaggio in questo forum , un saluto in particolare ad Andrea , che mi ha suggerito questo sito e spedito i chip

Da vari anni sto anche su

www.diyaudio.com come stefanobilliani .

Dunque son spinto a postare su questo topic a causa di questo piccolo lettore CD723 che uso ormai da tempo.

Ma le considerazioni delle quali mi accingo a scrivere arrivano dall'ascolto del Marantz CD67 mk2SE in particolare . A parte il fatto che considero il CD723 molto piu silenzioso del CD67 - e già questo mi fa automaticamente virare sul

723 , trovo dall'altro lato della vicenda che il Marantz lascia intravedere una maggior fluidità nel timing con vari effeti benefici , che se non fosse per il rumore potrebbero venir felicemente a galla .

Quindi dopo essermi posto alcune domande ho dato un'occhiata a come sono "motorizzati" ripsettivamente lo Saa7378 ( cd 723 ) e Saa7372 ( cd67 ). Entrambi i decoder hanno una cosa in comune: se l'input è un clock a 8.4672Mhz hanno bisogno di un PLL interno che moltiplica la frequenza . Con lo stesso valore di registro ( registro B ) l'input puo essere sia 8.4672Mhz che 33.8688Mz . Usando 8.4672 Mhz va attivato il PLL interno tramite SELPLL posto al valore " 1" .

Per usare anche la frequenza 16.9344 Mhz si rende necessario modificare il registro " B" che come sappiamo non è una cosa cosi immediata .

Bene , detto questo .. il CD67 lavora a 16.9344 con il PLL interno disattivato , ma il bello è che possiamo disattivare sto PLL anche nel CD723 - senza modificare il registro - solo settando SELPLL a "O" e utilizzando un Xo a 33.8688 Mhz . Se qualcuno facesse delle misure di jitter sui segnali del 723 son convinto che risulterebbero piu decenti nella soluzione senza PLL . Analogamente cosi com'è il 723 produce un suono un po "stressato " attribuibile a valori di jitter non ottimali... ed il CD67 "suona " meglio pur in quell'ambiente cosi rumoroso ...beh alcuni produttori discografici riportano spesso di come possa suonare bene un sistema con clock NON PLL !

Ho già ordinato da Tentlabs un Xo per lo scopo , il resto ve lo saprò raccontare dopo i test

Ultima cosa , a differenza di altri player il 723 a me sembra piu felice con segnali I2S e Xo attorno ai 1.4- 1.7 volt DC , cio per dire che il Tent Xo preferisco alimentarlo a3.3 volt in questa applicazione - stile DVD player

Stessa cosa per i circuiti di reclock .

Ok grazie per l'ascolto e a presto

Stefano

Inviato: 02 giu 2007, 20:59

da STEBIL

-il filtro digitale usa un PLL per ricavare una frequenza multipla di 8.4 Mhz per lavorare ed esiste la possibilità di usare un clock a 33.2 MHz disattivando il PLL interno. Sicuramente senza reclock ci sarebbe un vantaggio ma visto che riclocchiamo i dati non credo si abbiano grossi vantaggi

Ciao

Andrea

Originariamente inviato da andypairo - 27/10/2006 : 21:35:12

Ecco mi rendo ora conto rileggendo il thread che l'argomento è stato già sfiorato da Andrea proprio agli inizi .

Beh dopo ripetuti ascolti , credo che la mia personale scelta andrebbe ( e poi verificherò "sul campo " ) sulla situazione NO PLL , a dipendere da reclock oppure no . Anche perchè in tutta meditazione , non credo che il problema di questo PLL si rifletta direttamente tanto sulla qualità del BCK ( il quale è facilmente sostituibile dividendo o ricloccando ) ma tanto sul comportamento generico all'interno del chip decorder stesso , Data slicer . E poi uscite a 11 mhz per controlli esterni . Bisognerebbe andare a fondo all'interno dell'architettura del chip per spiegare bene. In ogni modo in modalità 4*Fs il formato funziona anche col BCK direttamente dall'XO , non v'è dubbio , e se attaccare il BCK direttamente all'XO da un senso di "sicurezza " non mi sembra risolvere alcuni problemi insiti di questo lettore Come dire che c'è effettivamente qualcosa d'altro che stressa .

Vi terrò informati del risultato .

Cha chao .

Stefano

Inviato: 02 giu 2007, 22:11

da andypairo

Innanzitutto benvenuto Stefano,

sono contento che sei approdato al nostro forum.

Ne approfitto per chiederti di spiegare in un post come hai modificato le alimentazioni del CD723, in modi che sia di riferimento per chi intendesse modificarlo.

Ho ancora la mail che mi hai mandato a novembre ma mancano dei dettagli e poi credo sia più giusto che sia tu a parlare del tuo lavoro

Ciao

Andrea

Inviato: 11 giu 2007, 20:29

da andypairo

Ecco la terza versione beta della PCB (tutto va ancora provato).

Ciao

Andrea

Attachment: SchemiPcbv3.zip ( 50057bytes )

Attachment: SchemiPcbv3.zip ( 50057bytes )

Inviato: 19 giu 2007, 22:50

da titano

Ti rispondo quì...avevo capito male, pensavo che volessi farla con tutti i componenti a montaggio superficiale, passivi compresi (tranne il tda1541a...)

Che faccio? Incido?

Marco

Inviato: 20 giu 2007, 00:56

da andypairo

A questo punto direi di sì ; )

Poi, una volta verificato il tutto possiamo pensare ad ulteriori modifiche.

Ciao

Andrea

Inviato: 20 giu 2007, 00:58

da titano

A questo punto direi di sì ; )

Poi, una volta verificato il tutto possiamo pensare ad ulteriori modifiche.

Ciao

Andrea

Originally posted by andypairo - 19/06/2007 : 19:56:04

C'è qualche pista interrotta e qualche appendice in eccesso. Puoi ricontrollare un attimo? Nascondi il layout componenti, dovresti notarle più facilmente

Marco

Inviato: 20 giu 2007, 03:12

da andypairo

In effetti non li avevo notati.

La pista va ricomposta ma per il resto credo si tratti di "cosmesi" legata a qualche piccolo spostamento. In pochi minuti si corregge.

Altre osservazioni?

Ciao

Andrea

Inviato: 06 ott 2007, 23:36

da andypairo

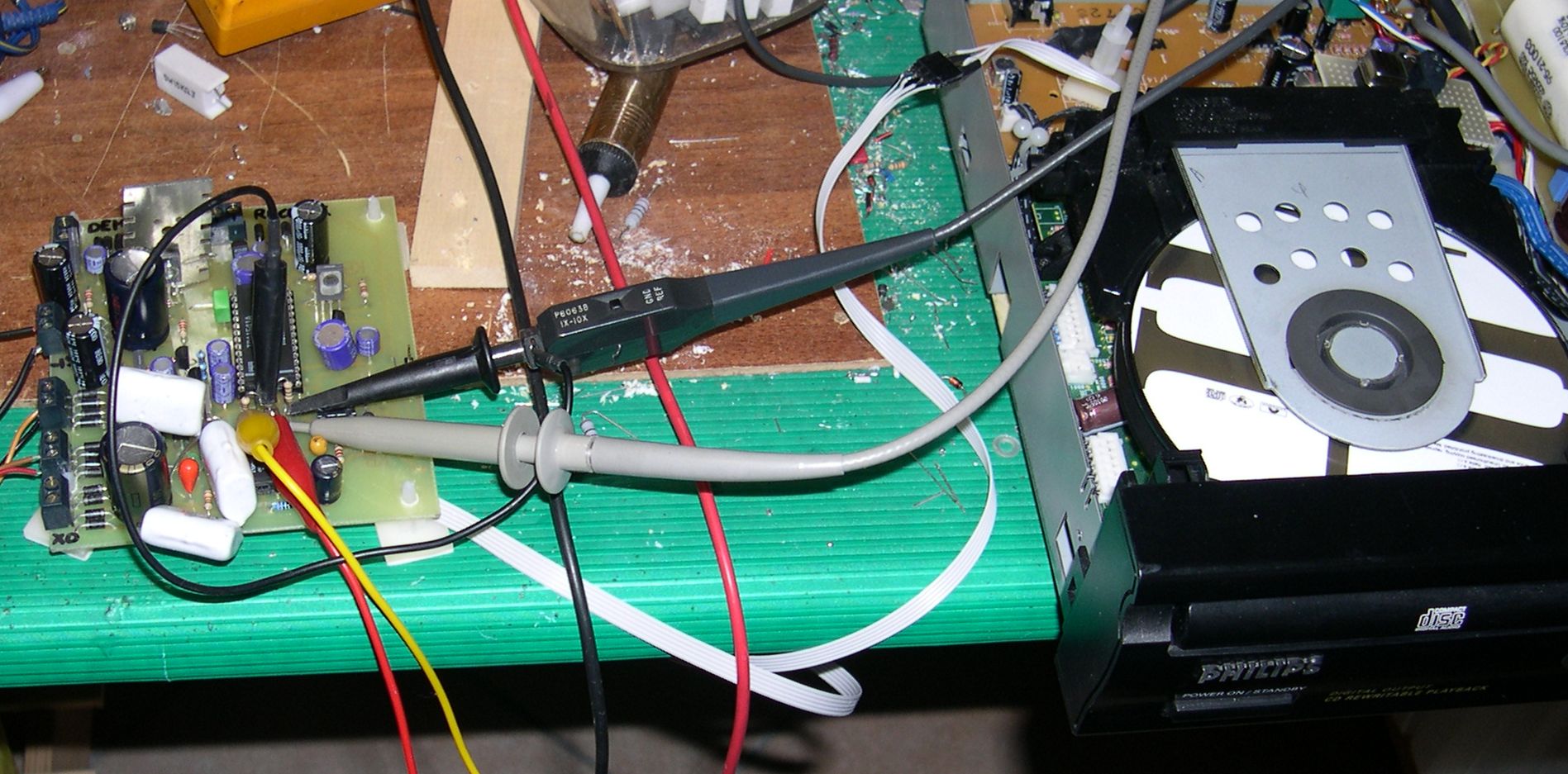

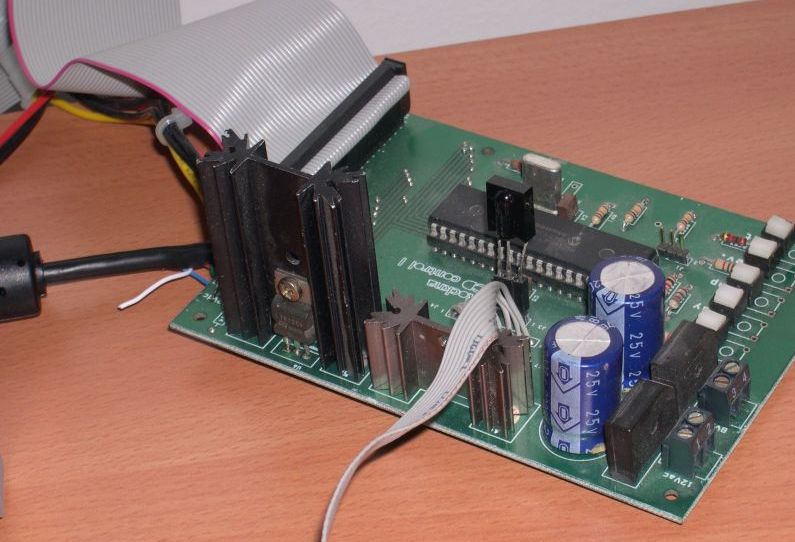

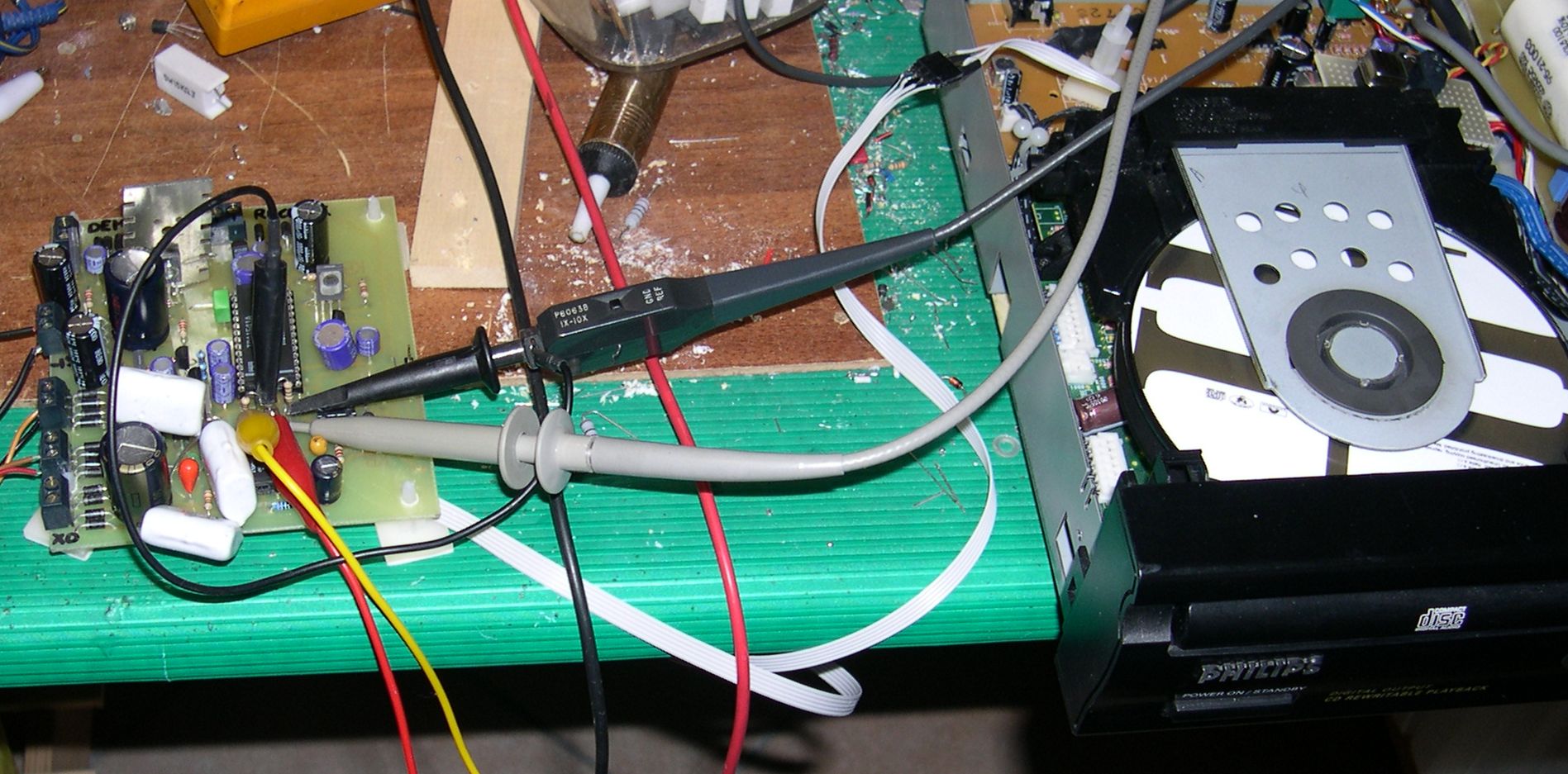

Dopo una lunga attesa siamo giunti ai primi test.

Fase 1: TDA nudo e crudo, pilotato dal CD723 hackerato.

Il formato è IIS ma la lunghezza dei frame 48Fs invece dei consueti 64.

Dopo un empasse iniziale.. funziona. Stadio I/V: R da 15 Ohm, poi diretto sul my_ref (ovviamente solo per prova).

Prime pics:

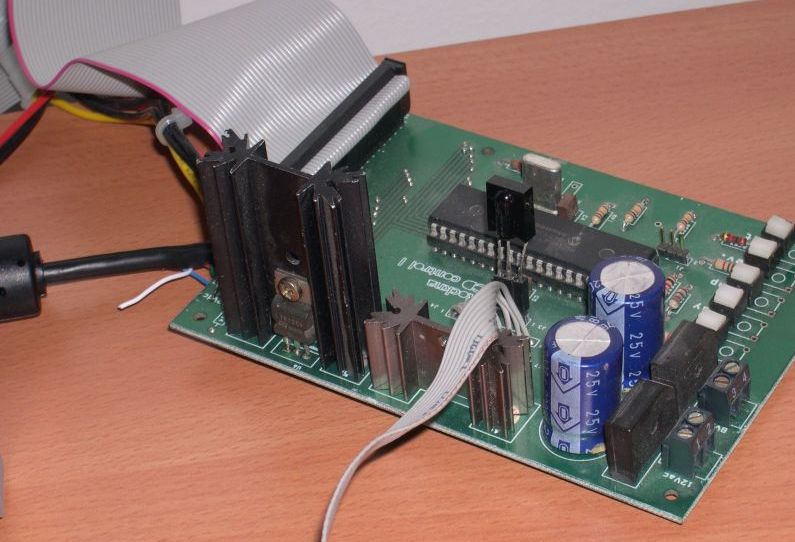

Inviato: 06 ott 2007, 23:48

da andypairo

Foto della PCB: notare i caps SMD per il decoupling del DEM. Per errore ho ricevuto dei 1210 al posto dei 1206 previsti e ho dovuto montarli sul fianco

Prossimo step: inserire il FLEA e il Tent XO.

Non prevedo problemi perchè adesso il CD usa già un XO, si tratta solo di collegarlo a quello sulla PCB.

A riguardo... ho preso una sòla.. comprati degli AD797 a otimo prezzo, arrivano e sono marchiati in maniera insolita... quando li provo non va nulla

Per ora uso un OPA627. PS se qualcuno ha dei Wima MKS2 da 3,3uF 50V o 63V o altre marche ma a passo max 7.5mm me ne servirebbero alcuni pezzi...

Ciao

Andrea

Inviato: 12 ott 2007, 14:31

da andypairo

Fase 2: inserito il tent XO e il Flea

Primo errore: devo aver involontariamente specchiato il pinout del Tent XO, per cui mi tocca montarlo dal lato saldature.

Per fortuna lavora ancora

Il player funziona ancora, per cui passo a inserire il reclock.

Secondo errore: ho dimenticato aperti i pin di clear dei flip flop, che vanno portati a +5.

Rimediato a questo errore il reclock va bene a 1xFs e 2xFs.

a 4xFs il BCK (che è alla stessa frequenza del clock) non viene ricloccato correttamente. Forse è legato al collegamento lungo e poco adatto (flat cable di circa 50cm, la forma d'onda è alquanto distorta). Verificherò.

Ciao

Andrea

Inviato: 13 ott 2007, 20:39

da andypairo

Ciao,

ho verificato col progettista della sezione di reclock e in effetti non è possibile riicloccare un segnale da 8.x Mhz con un clock della stessa frequenza. Esiste la possibilità di adoperare direttamente il clock come BCK (previa modifica dello stampato e inserzione di un jumper per la selezione) ma per il momento mi accontento di 1xFs e 2xFs.

Per ultimo ho inserito il DEM reclock, non prima di aver corretto un errore sullo stampato

e dopo alcuni tentativi (un elettrolitico inserito al contrario

, meno male che stavo usando l'alimentatore da banco e mi sono accorto subito) il tutto sembra funzionare correttamente. La frequenza del DEM reclock è l'unica possibile con il clock di partenza nel range attorno ai 200kHz (264kHz), pari a 6xFs.

Con un player che usi un data frame di 64xFs (IIS "standard") si potrebbe scegliere tra 4 e 8xFs.

L'esperimento alla fine sembra riuscito.

Ora devo mettere insieme un I/V come si deve e verificare alcune cosucce.

Per gli esperti di misure con l'oscillo (ho a disposizione un TEK 2246 100 Mhz - 4 canali e 2 sonde Tektronix 1:10 di cui una switchabile 1:1) che accortezze devo adoperare per ottenere delle misure attendibili sulla pulizia delle alimentazioni, sui ringing, ecc?

Lo chiedo perchè adesso se inverto le sonde (di cui una sola ha la massa collegata) il medesimo segnale viene visto in maniera piuttosto differente per quanto riguarda il rumore/oscillazione sovrapposti.

Conviene forse fare un collegamento unico alla boccola di terra ?

Ciao

Andrea

Inviato: 13 ott 2007, 21:33

da campedel

Per gli esperti di misure con l'oscillo (ho a disposizione un TEK 2246 100 Mhz - 4 canali e 2 sonde Tektronix 1:10 di cui una switchabile 1:1) che accortezze devo adoperare per ottenere delle misure attendibili sulla pulizia delle alimentazioni, sui ringing, ecc?

Lo chiedo perchè adesso se inverto le sonde (di cui una sola ha la massa collegata) il medesimo segnale viene visto in maniera piuttosto differente per quanto riguarda il rumore/oscillazione sovrapposti.

Conviene forse fare un collegamento unico alla boccola di terra ?

Originally posted by andypairo - 13/10/2007 : 15:39:32

Se sei interessato a misurare il rumore a frequenza elevata, usa una sonda alla volta, con la massa collegata il più vicino possibile al puntale della sonda (ad es. ai capi di un condensatore). Può essere utile attorcigliare il filo con il coccodrillo di massa attorno al puntale della sonda, ed eventualmente avvolgere il cavo della sonda attorno ad un nucleo di ferrite (quelli composti da due seminuclei tipo RM o ETD sono particolarmente comodi).

Ciao

Francesco

Inviato: 18 ott 2007, 13:49

da andypairo

Ciao,

ho dato un'occhiata alle alimentazioni e sono rimasto un po' interdetto: quasi tutti i 5V (a parte il +5 del TDA) presentano un'oscillazione a dente di sega intorno ai 5 kHz e ampiezza 30-40mV pk-pk. Il -15 presenta un'oscillazione più elevata e a frequenza inferiore.

Ricordo che sono regolatori shunt basati su TL431 pilotati da un CCS con singolo BJT (circa 60mA), pin ADJ bypassato verso il catodo del TL431 con OSCON da 22uF e in uscita OSCON da 220uF parallelato da 100nF SMD ceramico.

Ho provato a inserire una R tra il CCS e lo shunt senza risultati.

Parallelare caps di piccolo valore non serve, come nemmeno togliere il C di bypass di Vref.

Sostituendo il 220uF OSCON con un 100uF Panasonic FC non ho più oscillazione ma vedo chiaramente gli spike delle commutazioni degli IC (invisibili prima) con un ordine di grandezza di 20-30mV.

Domanda: guardando sul datasheet del TL431

http://focus.ti.com/lit/ds/symlink/tl431.pdf

a pagina 24 abbiamo il grafico di stabilità. Con 220uF dovrei essere più che a posto (col bypass su Vref in AC dobbiamo usare la curva A)... allora come mai mi fa questo scherzo?

Ciao

Andrea

Inviato: 18 ott 2007, 14:07

da campedel

Ricordo che sono regolatori shunt basati su TL431 pilotati da un CCS con singolo BJT (circa 60mA), pin ADJ bypassato verso il catodo del TL431 con OSCON da 22uF e in uscita OSCON da 220uF parallelato da 100nF SMD ceramico.

Originally posted by andypairo - 18/10/2007 : 08:49:43

Solitamente il TL431 deve essere bypassato tra ADJ e ANODO, non al catodo ... è un errore di battitura ?

Ciao

Francesco

Inviato: 18 ott 2007, 14:33

da andypairo

Inviato: 18 ott 2007, 15:19

da campedel

Non conoscevo la pagina di TNT, è la prima volta che vedo un'applicazione con il condensatore tra adj e catodo; peraltro mettere un condensatore in retroazione positiva non so quanto aiuti la stabilità ...

Ciao

Francesco

Inviato: 18 ott 2007, 22:36

da Giaime

Sostituendo il 220uF OSCON con un 100uF Panasonic FC non ho più oscillazione ma vedo chiaramente gli spike delle commutazioni degli IC (invisibili prima) con un ordine di grandezza di 20-30mV.

Originally posted by andypairo - 18/10/2007 : 08:49:43

Questo già ti dovrebbe dire tutto!

Il regolatore oscilla per la troppo piccola ESR del condensatore alla sua uscita... noterai che per tenerlo stabile (come da grafico di TNT-Audio) il condensatore all'uscita C1 deve avere un'ESR di 0.1ohm o superiore, il perchè viene spiegato qui:

http://www.national.com/an/AN/AN-1148.pdf

PS il TL431 (non farti fregare dal simbolo un po' diverso dal solito!) non è altro che il solito regolatore a 3 terminali, con error amp e pass element, tipo LM317 (non vorrei sbagliarmi, ma ad una rapida occhiata mi pare che quest'ultimo sia pure molto meglio, a giudicare dal plot di Bode del guadagno...). Questi dispositivi sono compensati a polo dominante e non possono garantirti chissà che prestazioni in AF, come noti dal fatto che, rendendo stabile il tuo regolatore, ecco apparire rumore di commutazione. Soluzione? Come regolatore usa un inseguitore di emettitore (ultimo schema qui

http://www.tnt-audio.com/clinica/regulators_noise3.html) e alimenta ogni chip con un gruppo RC o LC separato (ovviamente LC scelti di modo da minimizzare il ringing delle transizioni... il problema non è rendere pulita la linea che va al singolo chip, cosa tra l'altro impossibile a livello pratico, ma evitare che le commutazioni di un chip influenzino l'altro via l'alimentazione! Insomma la regola è separare, piuttosto che iper-regolare...).

Ciao!

Giaime Ugliano

Inviato: 18 ott 2007, 22:58

da andypairo

Sei sicuro che stiamo parlando della stessa cosa?

Il TL431 è un regolatore shunt, mica serie, per cui non dovrebbe soffrire dei problemi legati alla bassa ESR.

Normalmente è usato in quel modo, se poi vai a vedere il grafico da me indicato vedrai che sono richiesti un minimo di 5-10uF in uscita, senza però porre limiti in alto alla capacità nè alla ESR.

Ciao

Andrea

Inviato: 18 ott 2007, 23:15

da Giaime

Sei sicuro che stiamo parlando della stessa cosa?

Il TL431 è un regolatore shunt, mica serie, per cui non dovrebbe soffrire dei problemi legati alla bassa ESR.

Originally posted by andypairo - 18/10/2007 : 17:58:53

Non c'entra niente!

Se l'elemento d'uscita sia a pass element (regolatore serie) o in parallelo al carico (regolatore shunt) ciò che lo pilota è sempre un operazionale, e il tutto è comunque racchiuso in un loop di NFB, e la stabilità dipende fortemente da ciò che c'è attaccato all'uscita... ; )

Normalmente è usato in quel modo, se poi vai a vedere il grafico da me indicato vedrai che sono richiesti un minimo di 5-10uF in uscita, senza però porre limiti in alto alla capacità nè alla ESR.

Ciao

Andrea

Originally posted by andypairo - 18/10/2007 : 17:58:53

Occhio, quei grafici sono simulazioni, non misure reali... i modelli di SPICE dei regolatori a 3 terminali spesso (ho provato) non simulano correttamente l'instabilità dovuta alla bassa ESR del condensatore all'uscita. E comunque se noti nello schema di TNT-Audio R13 non è messa lì a caso... ; )

Prova ad usare un elettrolitico normale, commerciale, o un condensatore al tantalio solido, se non ricordo male nella AN1148 che ti ho linkato poco sopra sono quelli consigliati per risolvere questo tipo di problemi.

Ciao!

Giaime Ugliano

Inviato: 19 ott 2007, 03:32

da andypairo

Ciao,

devo ammettere che non avevo inquadrato bene il problema.

O forse mi sono fidato troppo di quello che ho visto nei vari circuiti in rete.

Dopotutto l'Adagio di T. Loesch usa proprio i TL431 con gli OS-CON (anche se di valore più piccolo).

La cosa strana è che il +5V del DAC non ha problemi...

Per le altre supply ho usato dei caps "scamuzzi" e un bypas leggero (0.1uF) sul pin Adj e le cose sono andate a posto.

Grazie.

Ciao

Andrea

Inviato: 19 ott 2007, 23:03

da Giaime

A disposizione!

Dai una chance al regolatore a gyrator. O emitter follower, o moltiplicatore di capacità, come diavolo lo vuoi chiamare. Funziona... fino alla ft del transistor, tipicamente piuttosto alta ; )

Ciao!

Giaime Ugliano

Inviato: 25 ott 2007, 15:49

da andypairo

Ciao,

in effetti i regolatori che citi erano in alternativa a quelli col TL431 ma non sono stati votati a sufficienza

La domanda però è: serve di più avere basso rumore o regolazione della linea?

Io non saprei rispondere, a parte "entrambi".

Per quanto riguarda l'ascolto: sono riuscito a fare un ascoltino, in pausa pranza approfittando dell'assenza di moglie e figlia: purtroppo è ancora "accrocchiato" con fili un po' sparsi e stadio I/V a tubi (resistenza da 15 Ohm, 6S45 choke loaded) che è troppo grosso per stare nel case.....

La prima impressione è abbastanza buona, con TDA "liscio".

Sembra essersi asciugato in basso (che risulta più articolato), come da aspettarsi col DEM reclock; per il resto veniva voglia di alzare il volume e riusciva a suonare ad alto livello (relativamente) senza suonare "forte".

Purtroppo l'ascolto è stato abbastanza frettoloso e con la bimba in giro non posso permettermi di fare ascolti prima delle 10 di sera (e pure a bassissimo volume....).

Per questo volevo vedere se riesco a farmi un I/V a stato solido al di sopra di ogni sospetto che stia nel contenitore originale... consigli?

Ciao

Andrea

Inviato: 25 ott 2007, 16:31

da marziom

Ciao,

in effetti i regolatori che citi erano in alternativa a quelli col TL431 ma non sono stati votati a sufficienza

La domanda però è: serve di più avere basso rumore o regolazione della linea?

Io non saprei rispondere, a parte "entrambi".

dalle ultime esperienze fatte sul mio DAC: serve avere isolamento tra le linee.

la regolazione a quelle frequenze va a putt., il rumore sulle linee digitali è relativamente poco dannoso...mentre sul DAC vero e proprio e sul ricevitore (che tu non hai) meglio qualcosa di pulito.

Per quanto riguarda l'ascolto: sono riuscito a fare un ascoltino, in pausa pranza approfittando dell'assenza di moglie e figlia: purtroppo è ancora "accrocchiato" con fili un po' sparsi e stadio I/V a tubi (resistenza da 15 Ohm, 6S45 choke loaded) che è troppo grosso per stare nel case.....

...

Per questo volevo vedere se riesco a farmi un I/V a stato solido al di sopra di ogni sospetto che stia nel contenitore originale... consigli?

ci siamo.....siamo arrivati insieme allo stesso scoglio

meglio! in due si raggiona meglio.

....quanti schemi vuoi?

comunque il mio dictat è impedenza di ingresso -> 0

marzio

_____________________

Se con 10 milioni di transistor non riesci a fare tutto sei un p**la!

Inviato: 26 ott 2007, 17:21

da andypairo

Quanti? Tutti!!

Scherzi a parte, io conosco e ho provato:

-Pass D1 (col TDA1545)

-OPA660 (col primo TDA1541A)

-AD844 (col terzo tda1541A)**

-I/V passivo seguito da E88CC con CCS (col secondo TDA1541A)*

-Diamond discreto di Pedja (col secondo TDA1541A)*

-I/V passivo con R da 15Ohm seguito da 6S45 choke loaded (quarto e ultimo! TDA1541A)